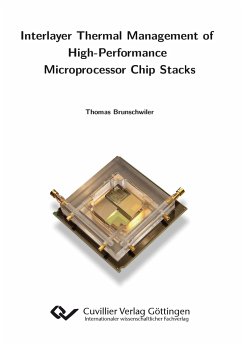

Vertical integration of integrated circuit dies offers tremendous opportunities from an architectural as well as from an economical standpoint. Memory proximity supports performance scaling, and might enable significant energy savings. Partitioning of the corresponding functionalities and technologies into individual tiers can improve yield and modularity substantially. The paradigm change of stacking active components has a direct impact on heat-removal concepts and is therefore the motivation of this thesis. A stack comprised of a single logic layer in combination with multiple memory dies was identified as the limit for traditional back-side heat removal. To minimize junction temperatures, a stacking sequence with the high heat-flux component in close proximity to the cold plate is proposed. Interlayer cooling is the only volumetric heat-removal solution that scales with the number of dies in the stack. Hence, the focus of this thesis has been to identify the potential of interlayer cooling and to provide a modeling framework. Fundamental heat-transfer building blocks, such as unit-cell geometries, fluid structure modulation, fluid focusing, as well as four-port fluid delivery supporting power-map-aware heat removal, are discussed. Moreover, the theoretical foundation was experimentally validated on resistively heated convective test cavities. Therefore, specific bonding and insulation schemes were developed. Finally, the interlayer cooling performance was demonstrated on a pyramid chip stack.