# PHYSICS AND TECHNOLOGY OF CRYSTALLINE OXIDE SEMICONDUCTOR CAAC-IGZO

# APPLICATION TO LSI

### Edited by Shunpei Yamazaki and Masahiro Fujita

WILEY SID

Series in Display Technology

# PHYSICS AND TECHNOLOGY OF CRYSTALLINE OXIDE SEMICONDUCTOR CAAC-IGZO

### Wiley-SID Series in Display Technology

### Series Editors: Anthony C. Lowe and Ian Sage

Display Systems: Design and Applications Lindsay W. MacDonald and Anthony C. Lowe (Eds.) Electronic Display Measurement: Concepts, Techniques, and Instrumentation Peter A. Keller Reflective Liquid Crystal Displays Shin-Tson Wu and Deng-Ke Yang Colour Engineering: Achieving Device Independent Colour Phil Green and Lindsay MacDonald (Eds.) Display Interfaces: Fundamentals and Standards Robert L. Myers Digital Image Display: Algorithms and Implementation Gheorghe Berbecel Flexible Flat Panel Displays Gregory Crawford (Ed.) Polarization Engineering for LCD Projection Michael G. Robinson, Jianmin Chen, and Gary D. Sharp Introduction to Microdisplays David Armitage, Ian Underwood, and Shin-Tson Wu Mobile Displays: Technology and Applications Achintya K. Bhowmik, Zili Li, and Philip Bos (Eds.) Photoalignment of Liquid Crystalline Materials: Physics and Applications Vladimir G. Chigrinov, Vladimir M. Kozenkov, and Hoi-Sing Kwok Projection Displays, Second Edition Matthew S. Brennesholtz and Edward H. Stupp Introduction to Flat Panel Displays Jiun-Haw Lee, David N. Liu, and Shin-Tson Wu LCD Backlights Shunsuke Kobayashi, Shigeo Mikoshiba, and Sungkyoo Lim (Eds.) Liquid Crystal Displays: Addressing Schemes and Electro-Optical Effects, Second Edition Ernst Lueder Transflective Liquid Crystal Displays Zhibing Ge and Shin-Tson Wu Liquid Crystal Displays: Fundamental Physics and Technology Robert H. Chen **3D** Displays Ernst Lueder OLED Display Fundamentals and Applications Takatoshi Tsujimura Illumination, Color and Imaging: Evaluation and Optimization of Visual Displays Peter Bodrogi and Tran Quoc Khanh Interactive Displays: Natural Human-Interface Technologies Achintya K. Bhowmik (Ed.) Addressing Techniques of Liquid Crystal Displays Temkar N. Ruckmongathan Fundamentals of Liquid Crystal Devices, Second Edition Deng-Ke Yang and Shin-Tson Wu

Modeling and Optimization of LCD Optical Performance Dmitry A. Yakovlev, Vladimir G. Chigrinov, and Hoi-Sing Kwok

# PHYSICS AND TECHNOLOGY OF CRYSTALLINE OXIDE SEMICONDUCTOR CAAC-IGZO APPLICATION TO LSI

Edited by

Shunpei Yamazaki Semiconductor Energy Laboratory Co., Ltd, Japan

Masahiro Fujita University of Tokyo, Japan

# WILEY

This edition first published 2017 © 2017 John Wiley & Sons, Ltd

#### Registered Office

John Wiley & Sons, Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, United Kingdom

For details of our global editorial offices, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wiley.com.

The right of the authors to be identified as the authors of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, except as permitted by the UK Copyright, Designs and Patents Act 1988, without the prior permission of the publisher.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

Designations used by companies to distinguish their products are often claimed as trademarks. All brand names and product names used in this book are trade names, service marks, trademarks or registered trademarks of their respective owners. The publisher is not associated with any product or vendor mentioned in this book.

Limit of Liability/Disclaimer of Warranty: While the publisher and authors have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. It is sold on the understanding that the publisher is not engaged in rendering professional services and neither the publisher nor the authors shall be liable for damages arising herefrom. If professional advice or other expert assistance is required, the services of a competent professional should be sought

### Library of Congress Cataloging-in-Publication Data

Names: Yamazaki, Shunpei, 1942– author. | Fujita, Masahiro, 1956– author.

Title: Physics and technology of crystalline oxide semiconductor CAAC-IGZO. Application to LSI / Shunpei Yamazaki, Masahiro Fujita.

Description: Chichester, West Sussex, United Kingdom : John Wiley & Sons, Ltd Registered office John Wiley & Sons Ltd, [2017] | Includes bibliographical references and index.

Identifiers: LCCN 2016025860 | ISBN 9781119247340 (cloth) | ISBN 9781119247432 (epub) | ISBN 9781119247425 (Adobe PDF)

Subjects: LCSH: Semiconductors–Materials. | Semiconductors–Characterization. | Gallium compounds. | Zinc compounds.

Classification: LCC TK7871.85 .Y357598 2016 | DDC 621.39/5–dc23 LC record available at https://lccn.loc.gov/2016025860

A catalogue record for this book is available from the British Library.

Set in 10/12pt Times by SPi Global, Pondicherry, India

10 9 8 7 6 5 4 3 2 1

# Contents

| A  | bout 1  | the Edi  | tors                                                              | x     |

|----|---------|----------|-------------------------------------------------------------------|-------|

| Li | st of   | Contril  | butors                                                            | xii   |

| Se | eries I | Editor's | s Foreword                                                        | xiii  |

| Pı | eface   | !        |                                                                   | XV    |

| A  | cknov   | vledgm   | ents                                                              | xviii |

| 1  | Intr    | oductio  | on                                                                | 1     |

|    | 1.1     | Overv    | iew of this Book                                                  | 1     |

|    | 1.2     | Backg    | pround                                                            | 3     |

|    |         | 1.2.1    | Typical Characteristics of CAAC-IGZO FETs                         | 3     |

|    |         | 1.2.2    | Possible Applications of CAAC-IGZO FETs                           | 4     |

|    | 1.3     | Summ     | nary of Each Chapter                                              | 7     |

|    | Refe    | erences  |                                                                   | 9     |

| 2  | Dev     | ice Phy  | sics of CAAC-IGZO FET                                             | 11    |

|    | 2.1     | Introd   | uction                                                            | 11    |

|    | 2.2     | Off-St   | ate Current                                                       | 14    |

|    |         | 2.2.1    | Off-State Current Comparison between Si and CAAC-IGZO FETs        | 14    |

|    |         | 2.2.2    | Measurement of Extremely Low Off-State Current                    | 16    |

|    |         | 2.2.3    | Theoretical Discussion with Energy Band Diagram                   | 23    |

|    |         | 2.2.4    | Conclusion                                                        | 28    |

|    | 2.3     | Subth    | reshold Characteristics                                           | 29    |

|    |         | 2.3.1    | <i>Estimation of</i> I <sub>cut</sub> by SS                       | 30    |

|    |         | 2.3.2    |                                                                   | 33    |

|    |         | 2.3.3    | Reproduction of Measured Value and Estimation of I <sub>cut</sub> | 35    |

|    |         | 2.3.4    | Conclusion                                                        | 38    |

| 2.4  | Techn    | ique for Controlling Threshold Voltage $(V_{\rm th})$                        | 39 |

|------|----------|------------------------------------------------------------------------------|----|

|      | 2.4.1    | V <sub>th</sub> Control by Application of Back-Gate Bias                     | 39 |

|      | 2.4.2    | N <sub>th</sub> Control by Formation of Circuit for Retaining Back-Gate Bias | 42 |

|      | 2.4.3    | <i>V<sub>th</sub> Control by Charge Injection into the Charge Trap Layer</i> | 45 |

|      | 2.4.4    | Conclusion                                                                   | 49 |

| 2.5  | On-St    | ate Characteristics                                                          | 49 |

|      | 2.5.1    | Channel-Length Dependence of Field-Effect Mobility                           | 50 |

|      | 2.5.2    | Measurement of Cut-off Frequency                                             | 59 |

|      | 2.5.3    | Summary                                                                      | 62 |

| 2.6  | Short-   | Channel Effect                                                               | 62 |

|      | 2.6.1    | Features of S-ch CAAC-IGZO FETs                                              | 63 |

|      | 2.6.2    | Effect of S-ch Structure                                                     | 70 |

|      | 2.6.3    | Intrinsic Accumulation-Mode Device                                           | 71 |

|      | 2.6.4    | Dielectric Anisotropy                                                        | 74 |

|      | 2.6.5    | Numerical Calculation of the Band Diagrams in IGZO FETs                      | 76 |

|      | 2.6.6    |                                                                              | 82 |

| 2.7  | 20-nm    | -Node CAAC-IGZO FET                                                          | 83 |

|      | 2.7.1    | TGSA CAAC-IGZO FET                                                           | 83 |

|      | 2.7.2    | Device Characteristics                                                       | 86 |

|      | 2.7.3    | Memory-Retention Characteristics                                             | 89 |

|      | 2.7.4    | Summary                                                                      | 92 |

| 2.8  | Hybri    | d Structure                                                                  | 92 |

|      | 2.8.1    | TGTC Structure                                                               | 93 |

|      | 2.8.2    | TGSA Structure                                                               | 94 |

|      | 2.8.3    | Hybrid Structure                                                             | 96 |

| App  | endix: ( | Comparison between CAAC-IGZO and Si                                          | 98 |

| Refe | erences  |                                                                              | 99 |

|      |          |                                                                              |    |

| 3 | NOSRAM |

|---|--------|

| 0 |        |

| NO  | SRAM                                                        | 102 |

|-----|-------------------------------------------------------------|-----|

| 3.1 | Introduction                                                | 102 |

| 3.2 | Memory Characteristics                                      | 103 |

| 3.3 | Application of CAAC-IGZO FETs to Memory and their Operation | 104 |

| 3.4 | Configuration and Operation of NOSRAM Module                | 106 |

|     | 3.4.1 NOSRAM Module                                         | 106 |

|     | 3.4.2 Setting Operational Voltage of NOSRAM Module          | 106 |

|     | 3.4.3 Operation of NOSRAM Module                            | 108 |

| 3.5 | Multilevel NOSRAM                                           | 108 |

|     | 3.5.1 4-Level (2 Bits/Cell) NOSRAM Module                   | 110 |

|     | 3.5.2 8-Level (3 Bits/Cell) NOSRAM Module                   | 112 |

|     | 3.5.3 16-Level (4 Bits/Cell) NOSRAM Module                  | 114 |

|     | 3.5.4 Stacked Multilevel NOSRAM                             | 119 |

| 3.6 | Prototype and Characterization                              | 120 |

|     | 3.6.1 2-Level NOSRAM                                        | 120 |

|     | 3.6.2 4-Level NOSRAM                                        | 128 |

|     | 3.6.3 8-Level NOSRAM                                        | 128 |

|     | 3.6.4 16-Level NOSRAM                                       | 129 |

|     |                                                             |     |

|   |              | 3.6.5 Comparison of Prototypes                                           | 133 |  |  |

|---|--------------|--------------------------------------------------------------------------|-----|--|--|

|   | Refe         | rences                                                                   | 136 |  |  |

| 4 | DO           | SRAM                                                                     | 137 |  |  |

|   | 4.1          | Introduction                                                             | 137 |  |  |

|   | 4.2          | Characteristics and Problems of DRAM                                     | 138 |  |  |

|   | 4.3          |                                                                          | 138 |  |  |

|   | 4.4          | Configuration and Basic Operation of DOSRAM                              | 139 |  |  |

|   |              | 4.4.1 Circuit Configuration and Operation of DOSRAM                      | 139 |  |  |

|   |              | 4.4.2 Hybrid Structure of DOSRAM                                         | 139 |  |  |

|   | 4.5          | Operation of Sense Amplifier                                             | 140 |  |  |

|   |              | 4.5.1 Writing Operation                                                  | 140 |  |  |

|   |              | 4.5.2 Reading Operation                                                  | 141 |  |  |

|   | 4.6          | Characteristic Measurement                                               | 143 |  |  |

|   |              | 4.6.1 Writing Characteristics                                            | 143 |  |  |

|   |              | 4.6.2 Reading Characteristics                                            | 144 |  |  |

|   |              | 4.6.3 Data-Retention Characteristics                                     | 145 |  |  |

|   |              | 4.6.4 Summary of 8-kbit DOSRAM                                           | 145 |  |  |

|   | 4.7          | Prototype DOSRAM Using 60-nm Technology Node                             | 140 |  |  |

|   | т./          | 4.7.1 Configuration of Prototype                                         | 147 |  |  |

|   |              | 4.7.2 Measurements of Prototype Characteristics                          | 147 |  |  |

|   |              | 4.7.3 Summary for Prototype DOSRAM                                       | 140 |  |  |

|   | 4.8          | Conclusion                                                               | 151 |  |  |

|   |              | erences                                                                  | 151 |  |  |

| 5 | СРІ          | I                                                                        | 153 |  |  |

| • |              | Introduction                                                             | 153 |  |  |

|   |              | Normally-Off Computing                                                   | 153 |  |  |

|   | 5.3          | CPUs                                                                     | 156 |  |  |

|   |              | 5.3.1 Flip-Flop (FF)                                                     | 158 |  |  |

|   |              | 5.3.2 8-Bit Normally-Off CPU                                             | 166 |  |  |

|   |              | 5.3.3 32-Bit Normally-Off CPU (MIPS-Like CPU)                            | 170 |  |  |

|   |              | 5.3.4 32-Bit Normally-Off CPU (ARM <sup>®</sup> Cortex <sup>®</sup> -M0) | 174 |  |  |

|   | 5.4          | CAAC-IGZO Cache Memory                                                   | 181 |  |  |

|   | References 1 |                                                                          |     |  |  |

| 6 | FPC          | SA                                                                       | 194 |  |  |

|   | 6.1          | Introduction                                                             | 194 |  |  |

|   | 6.2          | CAAC-IGZO FPGA                                                           | 195 |  |  |

|   |              | 6.2.1 Overview                                                           | 195 |  |  |

|   |              | 6.2.2 PRS                                                                | 197 |  |  |

|   |              | 6.2.3 PLE                                                                | 200 |  |  |

|   |              | 6.2.4 Prototype                                                          | 202 |  |  |

|   | 6.3          | Multicontext FPGA Realizing Fine-Grained Power Gating                    | 209 |  |  |

|   |              | 6.3.1 Overview                                                           | 209 |  |  |

|   |              | 6.3.2 Normally-Off Computing                                             | 209 |  |  |

|   |              | 6.3.3 Prototype                                                          | 216 |  |  |

|   | 6.4  | Subth   | reshold Operation of FPGA                                 | 226 |

|---|------|---------|-----------------------------------------------------------|-----|

|   |      | 6.4.1   | Overview                                                  | 226 |

|   |      | 6.4.2   | Subthreshold Operation                                    | 227 |

|   |      | 6.4.3   | Prototype                                                 | 234 |

|   | 6.5  | CPU ·   | + FPGA                                                    | 240 |

|   |      | 6.5.1   | Overview                                                  | 240 |

|   |      | 6.5.2   | CPU Computing                                             | 241 |

|   |      | 6.5.3   | CPU + GPU Computing                                       | 242 |

|   |      | 6.5.4   | CPU + FPGA Computing                                      | 243 |

|   |      | 6.5.5   | CAAC-IGZO CPU + CAAC-IGZO FPGA Computing                  | 246 |

|   | Refe | erences |                                                           | 247 |

| 7 | Ima  | ge Sen  | sor                                                       | 250 |

|   | 7.1  | Introd  | uction                                                    | 250 |

|   | 7.2  | Globa   | l Shutter Image Sensor                                    | 251 |

|   |      | 7.2.1   | Sensor Pixel                                              | 251 |

|   |      | 7.2.2   | Global and Rolling Shutters                               | 252 |

|   |      | 7.2.3   | Challenges Facing Adoption of Global Shutter              | 254 |

|   |      | 7.2.4   | CAAC-IGZO Image Sensor                                    | 255 |

|   | 7.3  | Image   | e Sensor Conducting High-Speed Continuous Image Capture   | 262 |

|   |      | 7.3.1   | Overview                                                  | 262 |

|   |      | 7.3.2   | Conventional High-Speed Continuous-Capturing Image Sensor | 263 |

|   |      | 7.3.3   | High-Speed Continuous-Capturing CAAC-IGZO Image Sensor    | 263 |

|   |      | 7.3.4   | Application to Optical Flow System                        | 276 |

|   | 7.4  | Motio   | on Sensor                                                 | 278 |

|   |      | 7.4.1   | Overview                                                  | 278 |

|   |      | 7.4.2   | Configuration                                             | 278 |

|   |      | 7.4.3   | Prototype                                                 | 283 |

|   |      | 7.4.4   | Sensor Pixel Threshold-Compensation Function              | 285 |

|   | Refe | erences |                                                           | 291 |

| 8 | Fut  | ure Ap  | plications/Developments                                   | 293 |

|   | 8.1  | Introd  | luction                                                   | 293 |

|   | 8.2  | RF D    | evices                                                    | 294 |

|   |      | 8.2.1   | Overview                                                  | 294 |

|   |      |         | NOSRAM Wireless IC Tag                                    | 294 |

|   |      |         | Application Examples of NOSRAM Wireless IC Tags           | 298 |

|   | 8.3  | X-Ray   | y Detector                                                | 303 |

|   |      | 8.3.1   | Outline                                                   | 303 |

|   |      | 8.3.2   | X-Ray Detection Principle                                 | 303 |

|   |      | 8.3.3   |                                                           | 304 |

|   |      | 8.3.4   | 1                                                         | 308 |

|   | 8.4  | CODI    |                                                           | 310 |

|   |      |         | Introduction                                              | 310 |

|   |      | 8.4.2   | Encoder/Decoder                                           | 311 |

|   |      | 8.4.3   | CAAC-IGZO CODEC                                           | 313 |

| 8.5    | DC-D          | C Converters                                                      | 314 |  |

|--------|---------------|-------------------------------------------------------------------|-----|--|

|        | 8.5.1         | Introduction                                                      | 314 |  |

|        | 8.5.2         | Non-hybrid DC–DC Converter                                        | 315 |  |

|        | 8.5.3         | Fabricated CAAC-IGZO Bias Voltage Sampling Circuit with Amplifier | 315 |  |

|        | 8.5.4         | Evaluation Results of Fabricated CAAC-IGZO Bias Voltage Sampling  |     |  |

|        |               | Circuit with Amplifier                                            | 317 |  |

|        | 8.5.5         | Proposed DC–DC Converter                                          | 318 |  |

| 8.6    | Analo         | g Programmable Devices                                            | 322 |  |

|        | 8.6.1         | Overview                                                          | 322 |  |

|        | 8.6.2         | Design                                                            | 322 |  |

|        | 8.6.3         | Prototype                                                         | 323 |  |

|        | 8.6.4         | Possible Application to Phase-Locked Loop                         | 330 |  |

| 8.7    | Neura         | l Networks                                                        | 330 |  |

|        | 8.7.1         | Introduction                                                      | 330 |  |

|        | 8.7.2         | Neural Networks                                                   | 330 |  |

|        | 8. <i>7.3</i> | CAAC-IGZO Neural Network                                          | 332 |  |

|        | 8.7.4         | Conclusion                                                        | 334 |  |

| 8.8    | Memo          | ry-Based Computing                                                | 335 |  |

| 8.9    | Backt         | cacking Programs with Power Gating                                | 339 |  |

| Refe   | erences       |                                                                   | 341 |  |

| Append | dix           |                                                                   | 343 |  |

| Index  | dex 345       |                                                                   |     |  |

# About the Editors

**Shunpei Yamazaki** received his Ph.D., ME, BE, and honorary degrees from Doshisha University, Japan, in 1971, 1967, 1965, and 2011, respectively, and is the founder and president of Semiconductor Energy Laboratory Co., Ltd. He invented a basic device structure of non-volatile memory known as "flash memory" in 1970 during his Ph.D. program. Yamazaki is a distinguished foreign member of the Royal Swedish Academy of Engineering Sciences and a founder of Kato & Yamazaki Educational Foundation. Yamazaki has published or co-published over 400 papers and conference presentations and is the inventor or co-inventor of over 6314 patents (Guinness World Record in 2011).

- 1967 Completed Master's Degree Program at Doshisha University Graduate School of Engineering

- 1970 Invented a basic device of flash memory (Japanese Patent No. 886343; Japanese Examined Patent Application Publication No. Sho50-36955)

- 1971 Received Ph.D. in Engineering from Doshisha University Graduate School Doctoral Program

Joined TDK Corporation (formerly TDK Electronics Co., Ltd.)

- 1980 Established Semiconductor Energy Laboratory Co., Ltd. and assumed position as president

- 1984 Awarded the Richard M. Fulrath Award by the American Ceramic Society (for research on MIS structure)

- 1995 Awarded the Medal with Dark Blue Ribbon from the Cabinet Office of the Japanese government (proceeds given to Japanese Red Cross Society) (awarded 6 times since 2015)

- 1997 Awarded the Medal with Purple Ribbon from the Cabinet Office of the Japanese government (for development of MOS LSI element technology)

- 2009 IVA (Royal Swedish Academy of Engineering Science) Foreign Member

- 2010 Awarded Okochi Memorial Technology Award from Okochi Memorial Foundation

- 2011 IEEE Life Fellow Received Honorary Doctor Degree of Culture from Doshisha University

Renewed his first Guinness World Record in 2004 (man holding the most patents in the world)

- 2015 Granted the title of "Friend of Doshisha" by Doshisha University

- 2015 SID Special Recognition Award for "discovering CAAC-IGZO semiconductors, leading their practical application, and paving the way to next-generation displays by developing new information-display devices such as foldable or 8K × 4K displays"

Masahiro Fujita received his Ph.D. in Information Engineering from the University of Tokyo in 1985 on his work on model checking of hardware designs by using logic programming languages. In 1985, he joined Fujitsu as a researcher and started to work on hardware automatic synthesis as well as formal verification methods and tools, including enhancements of BDD/ SAT-based techniques. From 1993 to 2000, he was director at Fujitsu Laboratories of America and headed a hardware formal verification group which was developing a formal verifier for real-life designs having more than several millions of gates. The developed tool has been used in production internally at Fujitsu and externally as well. Since March 2000, he has been a professor at VLSI Design and Education Center in the University of Tokyo. He has done innovative works in the areas of hardware verification, synthesis, testing, and software verification mostly targeting embedded software and web-based programs. He has been involved in a Japanese governmental research project for dependable system designs and has developed a formal verifier for C programs that could be used for both hardware and embedded software designs. The tool is now under evaluation jointly with industry with governmental support. He has authored and co-authored 10 books, and has more than 300 publications and has been given several awards from scientific societies. He has been involved as program and steering committee members in many prestigious conferences on CAD, VLSI designs, software engineering, and more. His current research interests include synthesis and verification of SoC (System on Chip), hardware/software co-designs targeting embedded systems and cyber physical systems, digital/analog co-designs, and formal analysis, verification, and synthesis of embedded programs.

# List of Contributors

### Shunpei Yamazaki (editor) Masahiro Fujita (editor)

In alphabetical order:

Takeshi Aoki Masami Endo **Hiroki Inoue** Takahiko Ishizu Masayuki Kimura Munehiro Kozuma Yoshiyuki Kurokawa Shuhei Maeda Daisuke Matsubayashi Shinpei Matsuda Takanori Matsuzaki Shuhei Nagatsuka Satoru Okamoto Yuki Okamoto Tatsuya Onuki Takashi Shingu Yutaka Shionoiri Kei Takahashi Toshihiko Takeuchi Masashi Tsubuku Naoaki Tsutsui Seiichi Yoneda

Semiconductor Energy Laboratory Co., Ltd. The University of Tokyo

Semiconductor Energy Laboratory Co., Ltd. Semiconductor Energy Laboratory Co., Ltd.

## Series Editor's Foreword

The convergence of personal electronic devices towards small, powerful and multifunctional platforms throws into relief the conflict for resources between the display and other system electronics. On the one hand, high-quality, high-resolution and bright displays not only provide an essential human interface, but are one of the decisive factors in attracting users to purchase a device and differentiate between different models. On the other hand, the display has no purpose without the electronic systems which control and supply content to it – functions which now require powerful, fast data processing and information storage capabilities. Both display and system electronics must share the limited energy stored in a small, lightweight battery, and achieving excellent performance from the whole device, combined with adequate battery life from a small package, is a central challenge.

In this volume, Dr. Yamazaki and Professor Fujita bring together a comprehensive account of how CAAC oxide semiconductors can contribute to the ecosystem of large-scale integrated electronics. Many of the developments presented here provide routes to making major powerconsumption savings in the operation of electronic systems. In other cases, performance improvements or new capabilities arise from the use of these CAAC oxide components: this is the case, for example, in the imaging sensors presented in Chapter 7 of this book.

The book you are holding is one of the three volumes planned by Dr. Yamazaki and his colleagues, to give a comprehensive overview of CAAC-IGZO technology. The first volume presents the basic science and technology of the materials: deposition conditions, structure, physical properties, and the physics and performance of the semiconductor devices using them. The origin of high carrier mobility and the exceptional low leakage current in CAAC-IGZO TFTs, as well as techniques for measuring it, are presented.

The third volume will describe in detail the application of CAAC oxides to display devices – LCD and OLED active matrix circuits, driver circuits and new technologies which apply particularly to flexible displays. Issues of stability and light sensitivity, which are of particular importance in displays, are thoroughly explored and routes to their solution are presented.

In the present volume, the application of CAAC-IGZO to LSI is presented. The book includes a thorough account of the TFT structures exploited and their fabrication, threshold control and switching characteristics, including their extremely low off-state current and

relative immunity to short-channel effects. Then, the application of these components to the most important and relevant electronic subsystems is described: memory, CPUs and FPGAs. The benefits available from CAAC devices in these systems are described – long-term data storage without refresh, higher memory densities and power reduction through adoption of normally-off logic. The design changes which can realise these benefits and the actual performance of circuits are described. In imaging sensors, the low leakage current of CAAC devices allows high-performance global shuttering and on-sensor image processing to be realised, bringing new capabilities to the devices. The volume concludes with an overview of further application fields, including RF tags, X-ray imaging and CODEC systems.

The authors and editors bring to their subject an outstanding breadth of expertise in the research and development of CAAC-IGZO materials, devices and systems, and their account of the subject should provide a definitive source for those seeking to understand and exploit the impact of this developing technology on modern electronics.

Ian Sage Malvern, UK, 2016

## Preface

Entering the 21st century, it seems that the growth of the electronics industry is hitting saturation level, even though it is the largest industry in the world. This is because the amount of energy used by people, which has already become enormous – as reflected in the abrupt climate change in recent years – is going to increase even more with its growth. Especially, the energy consumptions of cloud computing and electronic devices such as smartphones and supercomputers will continue to increase. Therefore, it is not an exaggeration to say that the development of new energy-saving devices has a direct influence on the continued existence of all mankind.

For this reason, we started extensive research on crystalline oxide semiconductors (OS), especially on a *c*-axis-aligned crystalline indium – gallium – zinc oxide (CAAC-IGZO) semiconductor. Due to the economic downturn in the aftermath of the Lehman Brothers' bankruptcy in the autumn of 2008, many companies withdrew from research on this subject, but I never gave up and our research in this area has continued to the present day. One of the most important characteristics of a field-effect transistor (FET) using this wide-gap semiconductor is that the off-state current is on the order of yoctoampère per centimeter ( $10^{-24}$ A/cm) (yocto is the smallest SI prefix), which is smaller than that of any other device measured so far. This characteristic effectively reduces the energy consumption, and thus we believe that it coincides with society's need to save energy.

It has been less than 10 years since I started researching and developing oxide semiconductors, but I think that proposing their effectiveness without delay is the first step toward a contribution to humanity. That is why I would like to introduce this book series *Physics and Technology of Crystalline Oxide Semiconductor*, consisting of *Fundamentals*, *Application to LSI*, and *Application to Displays*, even though I know that it cannot be said that every detail is completely covered in the book series.

The book series contains the discovery of CAAC-IGZO by me, Shunpei Yamazaki, one of the editors and authors thereof, as well as the research results on its application obtained at Semiconductor Energy Laboratory Co., Ltd. (SEL), where I serve as president. We have decided to write the experimental facts down in as much detail as possible, and publish models whose principles have not yet been verified. The reason is that I would like to give a couple of hints to readers – graduate students, on-site researchers, and developers – so that they can

conduct further R&D as soon as possible. For these reasons, as well as the limited number of pages, I would like you to accept my deepest apologies for not being able to publish all of the data in these books. Even after the publication of these three books about crystalline oxide semiconductors, I would like to continue making our CAAC-IGZO technology known to the public by conducting further research on it from both engineering and academic points of view.

This book covers a wide range of topics, such as the device physics of FETs using CAAC-IGZO and their applications to LSI.

In the past, Bell Laboratories published a set of books called *The Bell Telephone Laboratories series* about the invention of transistors and research results thereof, which accordingly spread the current concept of transistors throughout the world. We sincerely hope that our books will help to spread the CAAC-IGZO technology just as *The Bell Telephone Laboratories series* helped to popularize the concept of transistors. I think that CAAC-OS, especially CAAC-IGZO, still has many unexplored possibilities and thus more institutions and scientists should research it in cooperation with each other. I am expecting that the CAAC-IGZO which we discovered will flourish in the 21st century by publishing its physical properties and principles, as well as by applying it in the display and LSI fields, especially in energy-saving devices.

So far, we have made some efforts by submitting papers and giving presentations at various conferences about crystalline oxide semiconductors and OS FETs. However, we have never heard of another case where a ceramic was used for an active element on a mass-production basis in Si LSI or displays; thus, many companies (with the exception of Sharp Corporation) will face a lot of difficulties in terms of mass production. Note that a ceramic with an amorphous structure has been proposed before, but it was not put into practical use due to reliability problems. Especially, the great depression following 2008 made many companies quit their R&D of ceramics with an amorphous structure, which was deemed to be fruitless because a FET utilizing amorphous ceramic lacks reliability.

I, Shunpei Yamazaki, observed a TEM image of an IGZO film in front of a TEM screen to find a solution for the reliability issue. At that time, I discovered that a CAAC structure existed in the IGZO film. I thought that the problem of reliability could be solved by using this kind of material, and thus shifted the focus of our R&D to CAAC-IGZO. A FET using this CAAC-IGZO has a high level of reliability, which cannot be said of a FET which uses amorphous IGZO. Thus, a FET with CAAC-IGZO is excellent from a repeatability point of view in that it can be measured and evaluated stably, both on the material and device level. As a result of the stable measurement and evaluation, we discovered that the off-state current is on the order of yoctoamps per centimeter  $(10^{-24} \text{A/cm})$ , as mentioned above. Additionally, since IGZO has a wide solid-solution phase, we succeeded in fabricating FETs using CAAC-IGZOs having high mobilities of  $30 - 70 \text{ cm}^2/\text{V-s}$ , thus exceeding  $50 \text{ cm}^2/\text{V-s}$ , by changing the composition ratio and the device structure. A mobility equaling that of an LTPS-FET means that the CAAC-IGZO might be able to not only fight evenly with an LTPS-FET, but also outperform it in the industry. Furthermore, we tried to apply CAAC-IGZO FETs to LSI, something which has never been done before, and discovered that such a FET can operate with a channel length of just 20 – 60 nm.

Our data has been reviewed by many specialists, but it seems that to help people understand *the true value of the crystalline oxide semiconductor*, there is still a need to further explain the numerous issues concerning fundamental properties, which have not yet been fully understood. Moreover, a lot of people gave us the same advice: to help intellectuals grasp the whole picture

of the technology by publishing a series of at least three books (*Fundamentals, Application to LSI*, and *Application to Displays*). Accordingly, I decided to publish them. Note that almost the whole content of these books is based on our experimental data. Hence, please acknowledge SEL and Advanced Film Device Inc. (AFD Inc.), a subsidiary of SEL, as the sources of these books, unless otherwise specified.

During the creation of this book, many people helped and guided us. I would like to express my deepest appreciation especially to Dr. Masahiro Fujita, who has improved the research environment in the field of OS LSI, for being a co-editor of this book, *Application to LSI*, and for training the employees of SEL.

Moreover, during the research and development on which these books are based, as well as during the writing process, many young researchers at SEL also contributed. The names of all the authors involved can be found in the List of Contributors.

We would also like to extend our heartfelt thanks to Dr. Johan Bergquist, Dr. Michio Tajima, Mr. Yukio Maehashi, Mr. Takashi Okuda, and Mr. Jun Koyama for helping us with the writing of this book – by checking for errors and giving us a great deal of advice on how to improve the text.

I was blessed with support and cooperation from many outstanding individuals. I would like to add that I could not have finished these books in such a short period of time without the efforts of Dr. Ian Sage, a Wiley-SID book series editor, who suggested the publication of the books within this time, as well as Ms. Alexandra Jackson and Ms. Nithya Sechin of John Wiley & Sons, Ltd. Last but not least, I would like to express my sincere gratitude to those publishers and authors who allowed us to use their figures as references in these books.

> Shunpei Yamazaki President of Semiconductor Energy Laboratory Co., Ltd.

## Acknowledgments

First of all, we would like to thank **Dr. Johan Bergquist**, **Dr. Michio Tajima**, **Mr. Yukio Maehashi**, **Mr. Takashi Okuda**, and **Mr. Jun Koyama**, who encouraged us and gave valuable advice on writing manuscripts.

Furthermore, we would also like to thank many people in a variety of fields for providing data, cooperation in writing manuscripts and English translation, and all other aspects of this book.

Our heartfelt thanks to (in alphabetical order):

Ms. Mayumi Adachi Ms. Yukari Amano Mr. Yoshinobu Asami Mr. Yuji Egi Mr. Toshiya Endo Ms. Nana Fujii Ms. Ai Hattori Mr. Shinji Hayakawa Mr. Atsushi Hirose Mr. Ryota Hodo Mr. Mitsuhiro Ichijo Ms. Yasuko Iharakumi Dr. Kiyoshi Kato Dr. Shuichi Katsui Mr. Hajime Kimura Ms. Kyoko Kitada

Ms. Yuko Konno Mr. Masaki Koyama Mr. Motomu Kurata Mr. Tetsunori Maruyama Ms. Michiyo Mashiyama Mr. Hidekazu Miyairi Ms. Tomoko Nakagawa Mr. Hasumi Nomaguchi Mr. Takuro Ohmaru Mr. Naoki Okuno Ms. Yoko Otake Ms. Shiori Saga Mr. Masayuki Sakakura Mr. Naoya Sakamoto Mr. Yujiro Sakurada Mr. Shinya Sasagawa

Ms. Yu Sasaki Mr. Yuichi Sato Mr. Akihisa Shimomura Ms. Erika Takahashi Ms. Tamae Takano Mr. Yasuhiko Takemura Mr. Hikaru Tamura Mr. Tetsuhiro Tanaka Ms. Mika Tatsumi Ms. Yukiko Tojo Mr. Ryo Tokumaru Ms. Hitomi Tsurui Mr. Yuto Yakubo Mr. Naoto Yamade Ms. Chiaki Yamura and many others

> Shunpei Yamazaki Masahiro Fujita

# 1

# Introduction

### 1.1 Overview of this Book

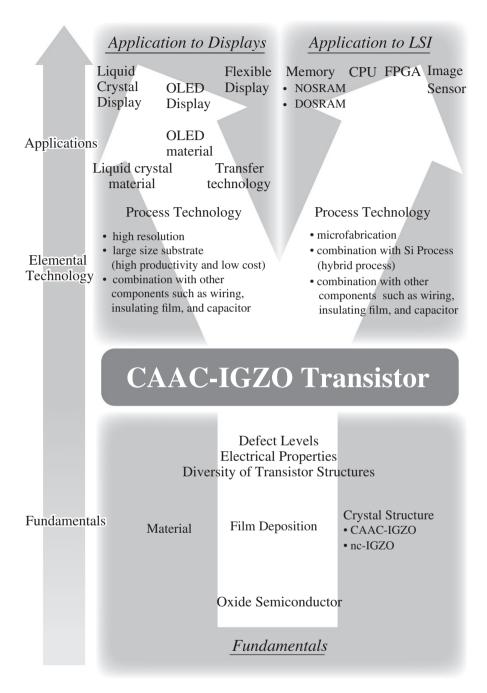

The three books in this series deal with *c*-axis-aligned crystalline indium–gallium–zinc oxide (CAAC-IGZO), an oxide semiconductor (see Figure 1.1): *Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Fundamentals* (hereinafter referred to as *Fundamentals*) [1], *Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSI* (this book, hereinafter referred to as *Application to LSI*), and *Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSI* (this book, hereinafter referred to as *Application to LSI*), and *Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to Displays* (hereinafter referred to as *Application to Displays*) [2]. *Fundamentals* describes, for example, the material properties of oxide semiconductors, the formation mechanism and crystal structure analysis of IGZO, the fundamental physical properties of CAAC-IGZO, the electrical characteristics of field-effect transistors (FETs) with CAAC-IGZO active layer (hereinafter referred to as CAAC-IGZO FETs), and comparisons between CAAC-IGZO and silicon (Si) FETs. *Application to Displays* introduces applications of the CAAC-IGZO FET technology to liquid crystal and organic light-emitting diode displays, describing the process flows and characteristics of the FETs, the driver circuits for displays, the technologies for high-definition, low-power, flexible displays, and so on.

This volume, *Application to LSI*, aims to introduce the applications of CAAC-IGZO FET technology to large-scale integration (LSI) and broadly and concisely review the device physics of CAAC-IGZO FETs. On the basis of the distinct material features of these FETs disclosed in *Fundamentals*, such FETs have an attractive application field in LSIs, in addition to the display applications described in *Application to Displays*. Not only focusing on oxide semiconductor material aspects, this book will also describe device design and fabrication using such materials, combination with other technologies, and specific applications (see Figure 1.2).

*Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSI*, First Edition. Edited by Shunpei Yamazaki and Masahiro Fujita.

<sup>© 2017</sup> John Wiley & Sons, Ltd. Published 2017 by John Wiley & Sons, Ltd.

Figure 1.1 Framework and summary of the book series

|   |             |                                                      | Base technology                                                                                                                | Problems to be solved                                                                                          | Evaluation                                                          |

|---|-------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|   | on          | Oxide<br>semiconductor<br>material                   | Defect control                                                                                                                 | Increase in purity<br>Impurity control                                                                         | Structural and<br>elemental analysis<br>Film quality<br>measurement |

|   |             | Oxide<br>semiconductor<br>device                     | Scale-down technology                                                                                                          | Optimization of processes<br>and device structures<br>Consistency with current<br>Si LSI manufacturing         | Device physics                                                      |

|   | Application | Combination<br>with other<br>technologies            | Combination with<br>passive elements<br>Hybrid<br>three-dimensional<br>structure of oxide<br>semiconductor and Si<br>elements. | Further reduction in F <sup>2</sup><br>Development of<br>lower-temperature<br>processes<br>Down-scaling issues | Electrical<br>characteristics                                       |

| 4 |             | Applications:<br>Internet of Thin<br>mobile devices, | gs (IoT), 8K television,<br>etc.                                                                                               | Matching interfaces and<br>performance with other<br>systems                                                   | Device size<br>Number of<br>processes<br>Power consumption          |

**Figure 1.2** Scope of this book. The symbol  $F^2$  means the square of the feature size F, used as an index of the memory cell size

Application examples of CAAC-IGZO FET technologies to LSIs are specifically described in the subsequent chapters.

### 1.2 Background

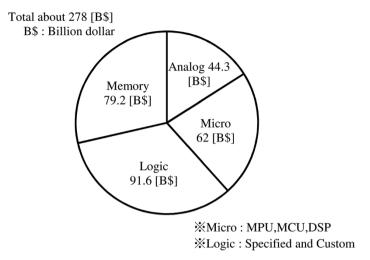

The integrated circuit (IC) has a huge market [3]. As shown in Figure 1.3, the total market size, including analog, micro, logic, and memory applications, is worth approximately 278 billion US dollars. Here, "micro" applications are microprocessor units (MPUs), microcontroller units (MCUs), and digital signal processors (DSPs); "logic" applications include specified logic and custom logic, such as field-programmable gate arrays (FPGAs) and application-specific integrated circuits (ASICs). CAAC-IGZO FETs address this vast IC market.

### 1.2.1 Typical Characteristics of CAAC-IGZO FETs

In the LSI field, reduction of power consumption has so far been achieved mainly by scaling down the FETs, employing advanced power management schemes, and more recently, sub-threshold driving. Si FETs are currently scaled down to very small technology nodes, for example, gate lengths as small as 14 and 16 nm [4]. Such aggressive downscaling causes

Figure 1.3 Market size of ICs in 2014. Source: Adapted from [3]

an increase in the FET off-state current (leakage current in the FET in the off state), which poses new obstacles to further reduction of system power [5].

As reported by Kato *et al.* [6], CAAC-IGZO FETs exhibit extremely low off-state current, for example,  $1.35 \times 10^{-22}$  A/µm (135 yA/µm, where y stands for yocto) for a FET with channel length/width of 3/50 µm. In contrast, the off-state current in a single-crystal Si (sc-Si) FET of the same structure and dimensions has an off-state current of  $1 \times 10^{-12}$  A/µm (1 pA/µm), i.e., 10 orders of magnitude larger. When CAAC-IGZO FETs are used in LSI devices, such as dynamic random access memory (DRAM), non-volatile memories, and central processing units (CPUs), their extremely low off-state current will therefore reduce the system power consumption tremendously.

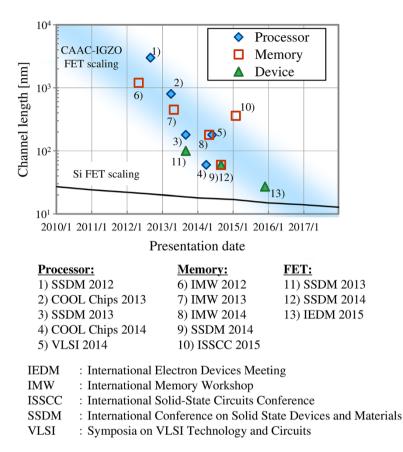

As reported by Matsubayashi *et al.* [7], CAAC-IGZO FETs with a channel node of 20 nm maintain the extremely low off-state current, despite the aggressive downscaling. Figure 1.4 shows the miniaturization progress of CAAC-IGZO and Si FETs during the past four to five years [8]. In the graph, the upper gray band corresponds to the achieved scaling values of CAAC-IGZO FETs, whereas the lower solid line shows the target scaling values of Si FETs disclosed by International Technology Roadmap for Semiconductors [9]. CAAC-IGZO FETs for processors, memories, and devices are denoted by diamond shapes, squares, and triangles, respectively. The number next to each mark corresponds to the conference shown below the graph where the device was disclosed. As shown, the scaling of CAAC-IGZO FETs gradually approaches that of Si FETs in recent years, so if the scaling continues to progress at this speed, it will catch up with that of Si FETs later in 2016 or 2017.

### 1.2.2 Possible Applications of CAAC-IGZO FETs

CAAC-IGZO FETs can be used in various LSIs (hereinafter called CAAC-IGZO LSIs), for example, in non-volatile memories [10–13], DRAMs [14], normally-off CPUs [15–17], FPGAs [18,19], and image sensors [20,21]. Non-volatile memories and DRAMs employing

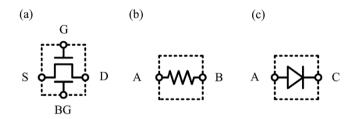

**Figure 1.5** (a) CAAC-IGZO FET, an active element with four terminals (source S, drain D, gate G, back gate BG); (b) resistive element, a passive element with two terminals; and (c) diode, a two-terminal passive element with non-linear characteristics

CAAC-IGZO FETs are called non-volatile oxide semiconductor random access memory (NOSRAM) and dynamic oxide semiconductor random access memory (DOSRAM), respectively.

A CAAC-IGZO FET is an active element with four terminals: source, drain, gate, and back gate, as shown in Figure 1.5. New memory technologies that have recently attracted attention

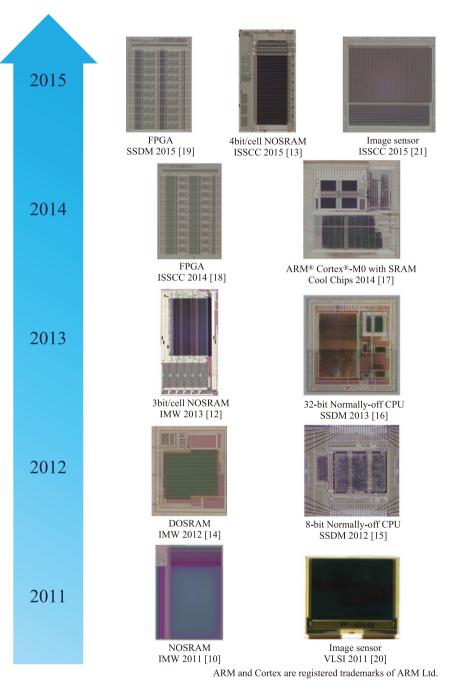

Figure 1.6 Examples of CAAC-IGZO LSIs fabricated between 2011 and 2015

Figure 1.7 Application examples of IoT. Source: Adapted from [22,23]

include magnetoresistive random access memory (MRAM), resistive random access memory (ReRAM), phase change random access memory (PCRAM), and ferroelectric random access memory (FeRAM). These are all passive elements with two terminals, whereas CAAC-IGZO FETs with their four terminals may lead to new applications.

Figure 1.6 shows photographs of LSIs with CAAC-IGZO FETs that have been fabricated so far. Below each photograph, the type of LSI and the name of the conference where it was presented are written.

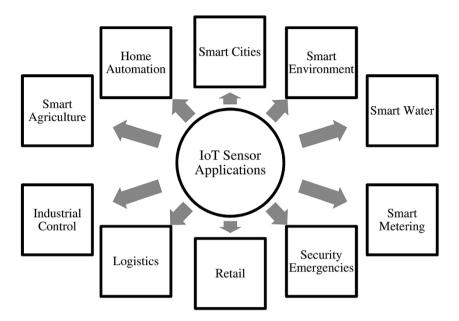

The concept of Internet of Things (IoT) is likely to be realized in the near future. In IoT, LSIs are used in various things to control them and collect and process information through the Internet. LSIs used for IoT should be inexpensive and autonomously powered, i.e., small in size and driven with low power, particularly in the idling state. It is therefore expected that CAAC-IGZO FETs, with their extremely low off-state current, will meet those requirements.

Janusz Bryzek, an advocate of IoT, proposes possible applications of IoT such as logistics, retail, security emergencies, and others (see Figure 1.7) [22,23]. He predicts that a total of one trillion sensors will be used in 2023 (i.e., he forecasts a huge possible market not only for the sensors themselves, but also for the necessary peripheral semiconductor circuits for preprocessing, temporary storage, and wireless transmission).

### **1.3 Summary of Each Chapter**

The device physics, structure, and fabrication process of CAAC-IGZO FETs are briefly explained in Chapter 2, whereas application examples in LSIs and the like are described in and after Chapter 3.

Chapter 2 also includes a review of *Fundamentals*, followed by a description of various CAAC-IGZO FET structures and their basic electrical characteristics, both in general and with emphasis on the low off-state current. CAAC-IGZO FETs are resistant to the downsizing-induced reduction in field-effect mobility or short-channel effect, and unlike sc-Si FETs, the off-state current of CAAC-IGZO FETs does not increase at high temperatures. The possibility of downscaling is illustrated, with results of a CAAC-IGZO FET with channel node of 20 nm [7]. The fabrication process flow of an actual CAAC-IGZO FET with a typical structure is also explained. A hybrid structure that vertically combines Si and CAAC-IGZO FETs is also introduced.

Chapter 3 deals with NOSRAM, where the CAAC-IGZO FET technology is applied to nonvolatile memories [10–13]. This non-volatile memory relies on the extremely low off-state current, and can operate at approximately 5 V (i.e., a quarter of the voltage of conventional flash memories). NOSRAM also exhibits an excellent write endurance. While conventional flash memory has a write endurance of approximately 10,000 cycles, NOSRAM endures one trillion writes, achieving a ten-million-fold increase. In addition, the electric potentials can be applied directly to the memory cell during data writing, thus providing accurate control over the accumulated electric charge. Therefore, NOSRAM enables multiple bits in one cell.

Chapter 4 presents DOSRAM in which the CAAC-IGZO FET technology is applied to the DRAM memory cell [14]. Compared with DRAM involving Si, DOSRAM features a long data retention period because the charge stored in the capacitor is hardly lost owing to the extremely low off-state current. Consequently, it requires less frequent refresh operations and therefore consumes less power than its Si FET-based equivalent. For the same reason, electric charges in a capacitor can be stored for a long time even at low capacitance. Accordingly, the capacitance required for data retention may be reduced, which is advantageous in miniaturization.

Chapter 5 describes a normally-off CPU deploying CAAC-IGZO FETs [15–17]. Similar to power gating, the power supply to a circuit stops when unused (the circuit switches to sleep mode) in a normally-off CPU, resulting in low power consumption. When a CPU circuit comprising Si FETs is subject to a power gating operation, there is an overhead in power consumption and performance due to saving and restoring of storage elements in the circuit. Consequently, power gating in short intervals has been problematic because the average CPU power consumption would increase instead. In contrast, a normally-off CPU implemented with CAAC-IGZO FETs reduces the overhead power consumption dramatically by exploiting the extremely low off-state current characteristics of CAAC-IGZO FETs, and shortens the time required for backup and recovery.

Chapter 6 provides an example wherein CAAC-IGZO FETs are applied to FPGAs [18,19]. An FPGA is an LSI that a user can configure after manufacture. In conventional FPGAs, the circuit configuration information is stored in a static random access memory (SRAM) that is used as configuration memory, but SRAM data are generally lost when the power is turned off. Consequently, setting information needs to be stored in the configuration memory every time the power is back on. If a non-volatile memory using a CAAC-IGZO FET replaces this SRAM, setting information is retained even when the power is turned off; thus, the memory does not need restoring in the configuration memory. Moreover, the area and power consumption compared with SRAM may be reduced. Therefore, the incorporation of a CAAC-IGZO FET is expected to produce an FPGA with higher density and lower power consumption. A power gating function can easily be implemented in FPGAs; consequently, turning off unused circuits

may further reduce power consumption. Normally-off operation suitable for fine-grained multicontext structures is also possible by developing the above-mentioned features. Chapter 6 also introduces FPGAs with subthreshold operation, further reducing the power consumption via the lower operating voltage. Finally, the potential development of high-performance computing by combining an FPGA and a CPU, which has recently attracted extensive interest, is discussed.

Chapter 7 presents an example of an image sensor that uses CAAC-IGZO FETs [20,21]. Many of the existing complementary metal–oxide semiconductor (CMOS) image sensors use a rolling shutter mode whereby sensor pixels sequentially capture imaging data row by row. However, this mode exhibits a delay between first and last capturing sensor pixels. Therefore, a fast-moving object yields a distorted image. This delay occurs because captured data get leaked over time and are required to be read out immediately after their capture. When CAAC-IGZO FETs are introduced in an image sensor, the extremely low off-state current of the FETs enables the implementation of a global shutter mode whereby all sensor pixels simultaneously capture data. This off-state current also allows sensor pixels to retain captured data until readout, regardless of any difference in readout timing. Using multiple retention nodes in each sensor pixel allows multiple capture with very short shutter times, an attractive feature in machine vision. Adding an image difference detection function to the sensor pixel gives a motion sensor that performs detection of changes with respect to a reference frame in addition to normal imaging.

Chapter 8 presents other examples of CAAC-IGZO FET applications, demonstrating the versatility of this device. These examples include radio-frequency devices, X-ray detectors, encoder–decoders (CODECs), DC–DC converters (DC denotes direct current), analog programmable devices, and neural networks that may find use in various environments. Further, memory-based computing and an ultra-efficient power gating mechanism are presented.

LSIs with CAAC-IGZO have characteristics of very low off-state current and the associated reduction in system power consumption suggests that CAAC-IGZO LSIs may entirely replace Si LSIs in some applications.

### References

- Yamazaki, S. and Kimizuka, N. (in press) Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Fundamentals. New York: John Wiley.

- [2] Yamazaki, S. and Tsutsui, T. (in press) Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to Displays. New York: John Wiley.

- [3] WSTS (2015) The Final Semiconductor Market Figures for 2014. World Semiconductor Trade Statistics.

- [4] ITRS (2013) Overall Roadmap Technology Characteristics (ORTC) Table. International Technology Roadmap for Semiconductors.

- [5] ITRS (2013) Process Integration, Devices, and Structures Summary. International Technology Roadmap for Semiconductors.

- [6] Kato, K., Shionoiri, Y., Sekine, Y., Furutani, K., Hatano, T., Aoki, T., et al. (2012) "Evaluation of off-state current characteristics of transistor using oxide semiconductor material, indium–gallium–zinc oxide," *Jpn. J. Appl. Phys.*, 51, 021201. http://doi.org/10.1143/JJAP.51.021201

- [7] Matsubayashi, D., Asami, Y., Okazaki, Y., Kurata, M., Sasagawa, S., Okamoto, S., et al. (2015) "20-nm-Node trench-gate-self-aligned crystalline In–Ga–Zn-oxide FET with high frequency and low off-state current," *IEEE IEDM Tech. Dig.*, 141. http://doi.org/10.1109/IEDM.2015.7409641

- [8] Yamazaki, S. (2016) "Unique technology from Japan to the world super low power LSI using CAAC-OS." Available at: www.umc.com/2015\_japan\_forum/pdf/20150527\_shunpei\_yamazaki\_eng.pdf [accessed February 11, 2016].

- [9] ITRS (2009) Table FEP2: High Performance Device Technical Requirements. Available at: www.dropbox.com/ sh/ia1jkem3v708hx1/AAB6fSsJmdHaQNEu538i9gKNa/2009%20Tables%20%26%20Graphs/FEP/2009Tables\_ FEP2.xls?dl=0 [accessed February 19, 2016].

- [10] Matsuzaki, T., Inoue, H., Nagatsuka, S., Okazaki, Y., Sasaki, T., Noda, K., et al. (2011) "1Mb Non-volatile random access memory using oxide semiconductor," Proc. IEEE Int. Memory Workshop, 185. http://doi.org/ 10.1109/IMW.2011.5873242

- [11] Inoue, H., Matsuzaki, T., Nagatsuka, S., Okazaki, Y., Sasaki, T., Noda, K., et al. (2012) "Nonvolatile memory with extremely low-leakage indium–gallium–zinc-oxide thin-film transistor," *IEEE J. Solid-State Circuits.*, 47, 2258. http://doi.org/10.1109/JSSC.2012.2198969

- [12] Nagatsuka, S., Matsuzaki, T., Inoue, H., Ishizu, T., Onuki, T., Ando, Y., et al. (2013) "A 3bit/cell nonvolatile memory with crystalline In–Ga–Zn–O TFT," Proc. IEEE Int. Memory Workshop, 188. http://doi.org/10.1109/ IMW.2013.6582131

- [13] Matsuzaki, T., Onuki, T., Nagatsuka, S., Inoue, H., Ishizu, T., Ieda, Y., et al. (2015) "A 128kb 4b/cell nonvolatile memory with crystalline In–Ga–Zn Oxide FET using Vt cancel write method," Int. Solid-State Circuits Conf. Dig. Tech. Pap., 306. http://doi.org/10.1109/ISSCC.2015.7063048

- [14] Atsumi, T., Nagatsuka, S., Inoue, H., Onuki, T., Saito, T., Ieda, Y., et al. (2012) "DRAM using crystalline oxide semiconductor for access transistors and not requiring refresh for more than ten days," Proc. IEEE Int. Memory Workshop, 99. http://doi.org/10.1109/IMW.2012.6213660

- [15] Ohmaru, T., Yoneda, S., Nishijima, T., Endo, M., Dembo, H., Fujita, M., et al. (2012) "Eight-bit CPU with non-volatile registers capable of holding data for 40 days at 85°C using crystalline In–Ga–Zn oxide thin film transistors," Ext. Abstr. Solid. State. Dev. Mater., 1144. http://doi.org/10.7567/SSDM.2012.J-5-2

- [16] Sjökvist, N., Ohmaru, T., Furutani, K., Isobe, A., Tsutsui, N., Tamura, H., et al. (2013) "Zero area overhead state retention flip flop utilizing crystalline In–Ga–Zn oxide thin film transistor with simple power control implemented in a 32-bit CPU," Ext. Abstr. Solid. State. Dev. Mater., 1088. http://doi.org/10.7567/SSDM.2013.M-6-4

- [17] Tamura, H., Kato, K., Ishizu, T., Uesugi, W., Isobe, A., Tsutsui, N., et al. (2014) "Embedded SRAM and Cortex-M0 core using a 60-nm crystalline oxide semiconductor," *IEEE Micro*, 34, 42. http://doi.org/10.1109/ MM.2014.96

- [18] Aoki, T., Okamoto, Y., Nakagawa, T., Ikeda, M., Kozuma, M., Osada, T., et al. (2014) "Normally-off computing with crystalline InGaZnO-based FPGA," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, 502. http://doi.org/ 10.1109/ISSCC.2014.6757531

- [19] Kozuma, M., Okamoto, Y., Nakagawa, T., Aoki, T., Kurokawa, Y., Ikeda, T., et al. (2015) "180-mV Subthreshold operation of crystalline oxide semiconductor FPGA realized by overdrive programmable power switch and programmable routing switch," Ext. Abstr. Solid State Dev. Mater., 1174.

- [20] Aoki, T., Ikeda, M., Kozuma, M., Tamura, H., Kurokawa, Y., Ikeda, T., et al. (2011) "Electronic global shutter CMOS image sensor using oxide semiconductor FET with extremely low off-state current," Symp. IEEE Symp. VLSI Technol. Dig. Tech. Pap., 175.

- [21] Ohmaru, T., Nakagawa, T., Maeda, S., Okamoto, Y., Kozuma, M., Yoneda, S., *et al.* (2015) "25.3 μW at 60 fps 240 × 160-Pixel vision sensor for motion capturing with in-pixel non-volatile analog memory using crystalline oxide semiconductor FET," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, 118.

- [22] TSenser Summit (2016) Genesis of TSensor. Available at: www.tsensorssummit.org/genesisoftsensor.html [accessed February 11, 2016].

- [23] Libelium Comunicaciones Distribuidas S.L. (2016) 50 Sensor applications for a smarter world. Available at: www.libelium.com/top\_50\_iot\_sensor\_applications\_ranking [accessed February 11, 2016].

# 2

# Device Physics of CAAC-IGZO FET

### 2.1 Introduction

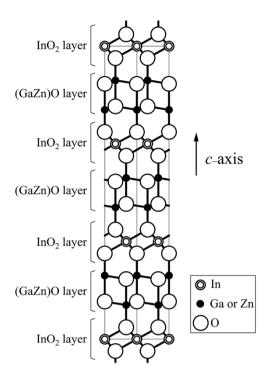

Kimizuka and Mohri [1] first synthesized an indium–gallium–zinc oxide (InGaZn oxide, hereinafter referred to as IGZO) in the 1980s, and revealed its crystal structure. In an IGZO crystal, repeat units, each having an InO<sub>2</sub> layer and a (GaZn)O layer, are periodically stacked to form a layered structure in a phase-equilibrium state (see Figure 2.1) [2]. In 1995, Orita *et al.* [3] examined the conduction characteristics and bandgap of a bulk InGaZnO<sub>4</sub> crystal with an ytterbium iron oxide (YbFe<sub>2</sub>O<sub>4</sub>) structure and reported that InGaZnO<sub>4</sub> is preferable as a transparent conductive material. Furthermore, Nomura *et al.* [4–6] made a single-crystal IGZO film on an yttria-stabilized zirconia (YSZ) substrate using reactive solid-phase epitaxy with heat treatment at 1400°C; they used the film as an active layer of a field-effect transistor (FET) and reported the FET characteristics. However, a FET with single-crystal IGZO as an active layer has not been put into practical use as of 2016.

Yamazaki *et al.* [7] reported a unique IGZO film with a crystal structure different from that of a single-crystal or polycrystalline IGZO, called a *c*-axis-aligned crystalline IGZO (CAAC-IGZO) film. An InGaO<sub>3</sub>(ZnO) crystal in the CAAC-IGZO film has the YbFe<sub>2</sub>O<sub>4</sub> structure (see *Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Fundamentals* [8] (hereinafter referred to as *Fundamentals*) for the details). In CAAC-IGZO, the *c*-axes of the crystals are aligned almost perpendicular to the CAAC-IGZO film surface, while the *a*-*b* planes are randomly oriented. In addition, there are no clear grain boundaries between the crystals. Formation of CAAC-IGZO does not require the high temperature of single-crystalline IGZO synthesis (1400°C, see Nomura *et al.* [4]). In addition, instead of epitaxial growth that slowly forms a film, high-speed sputtering can be used for the formation of CAAC-IGZO A FET having CAAC-IGZO as an active layer (hereinafter referred to as a CAAC-IGZO FET) is characterized by: (1) a low density of defect states due to its crystallinity [9], which offers stable

*Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSI*, First Edition. Edited by Shunpei Yamazaki and Masahiro Fujita.

<sup>© 2017</sup> John Wiley & Sons, Ltd. Published 2017 by John Wiley & Sons, Ltd.

**Figure 2.1** Crystal structure of IGZO [InGaO<sub>3</sub>(ZnO)<sub>*m*</sub>]. InO<sub>2</sub> layers and (GaZn)O layers are periodically stacked to form a layered structure

characteristics; (2) an extremely low off-state current of yoctoamp order (yA/ $\mu$ m, y = 10<sup>-24</sup>) [10]; and (3) strength against the short-channel effect [11] (here, "off-state current" means the leakage current in the off state). Liquid crystal displays using CAAC-IGZO FETs in the back-planes are already being mass produced [12].

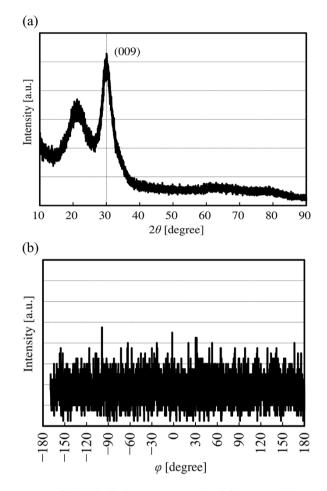

Figure 2.2 shows X-ray diffraction (XRD) spectra of a CAAC-IGZO film. The XRD spectrum in Figure 2.2(a) shows a peak of (009) indicating alignment of the *c*-axes of InGaO<sub>3</sub>(ZnO) crystals almost perpendicular to the film surface. In Figure 2.2(b), no diffraction peak is observed in the *a*–*b* plane, suggesting no orientation of the crystal *a*–*b* planes with respect to the film surface (see *Fundamentals* [8] for further details on XRD).

The use of CAAC-IGZO FETs in LSIs proceeds similarly in the display field [13–16]. Miniaturized CAAC-IGZO FETs in an LSI also have the above-mentioned characteristics. The offstate current of a CAAC-IGZO switching FET can be extremely low, which leads to extremely low power consumption by the LSI.

This chapter explains the device physics of a CAAC-IGZO FET. In Section 2.2, its extremely low off-state current will be described. In addition to the basic electrical characteristics, a comparison with a silicon (Si) FET is shown to demonstrate how low the off-state current of the CAAC-IGZO FET is. In fact, it is lower than the detection limit of a normal current-measurement instrument  $(10^{-13} \text{ A})$ , so an original measurement method had to be developed to measure this ultra-low off-state current.

Figure 2.2 XRD spectra of CAAC-IGZO. Source: Reprinted from [7], with permission from Wiley

In Section 2.3, a calculation method for estimating off-state currents lower than the detection limit of conventional devices, on the basis of transfer characteristics, is described. This method enables the estimation of  $I_{\text{cut}}$  (a drain current value  $I_{\text{d}}$  at a gate voltage  $V_{\text{g}}$  of 0 V) below the detection limit (10<sup>-13</sup> A). Here, shifting the threshold voltage  $V_{\text{th}}$  of a CAAC-IGZO FET allows the acquisition of a lower  $I_{\text{cut}}$  value. The calculation method can be used to find out how much  $V_{\text{th}}$  should be shifted to obtain a desired  $I_{\text{cut}}$  value (i.e., the value required for a particular CAAC-IGZO FET application).

In Section 2.4, a technique for controlling the threshold voltage ( $V_{th}$ ) of a CAAC-IGZO FET is described. The dynamic control of the FET's  $V_{th}$  is important not only for a reduction in variation of FET characteristics, but also for use of the extremely low off-state current of the CAAC-IGZO FET in LSI.

Section 2.5 explains the on-state current characteristics of a CAAC-IGZO FET. Although the electron mobility of a CAAC-IGZO FET is much lower than that of a Si FET, the difference in field-effect mobility is reduced for downscaled FETs. While a CAAC-IGZO FET with a

channel length (*L*) of 1  $\mu$ m has a field-effect mobility of approximately 10 cm<sup>2</sup>/*V*-s (i.e., 100 times lower than that of a Si FET), miniaturized Si FETs exhibit an increased drift field strength, which accelerates electrons, hence turning them into hot electrons. Hot electrons, in turn, generate phonons, and their drift velocity becomes saturated. That is, the speed of the electrons becomes saturated in a Si FET as the channel gets shorter. In CAAC-IGZO FETs, on the contrary, electrons are not easily accelerated, and do not easily become hot electrons; therefore, a saturation in drift velocity does not occur to the same extent as in a Si FET. As a result, the difference in field-effect mobility versus Si decreases by downscaling. This suggests that CAAC-IGZO FET, if sufficiently small, can replace Si FETs in LSIs.

In Section 2.6, we present a measure to be used against the short-channel effect of a CAAC-IGZO FET. A surrounded-channel (S-ch) structure gives small characteristic degradation. For example, even when a FET has a channel as short as 30 nm and its gate insulator has a thickness as large as 11 nm in equivalent oxide thickness (EOT), characteristic degradation hardly occurs with the S-ch structure.

Section 2.7 introduces a recent scaled-down CAAC-IGZO FET. The CAAC-IGZO FET with a 20-nm node has a cut-off frequency of 34 GHz. In addition, even in the scaled-down FET, the off-state current is extremely low.

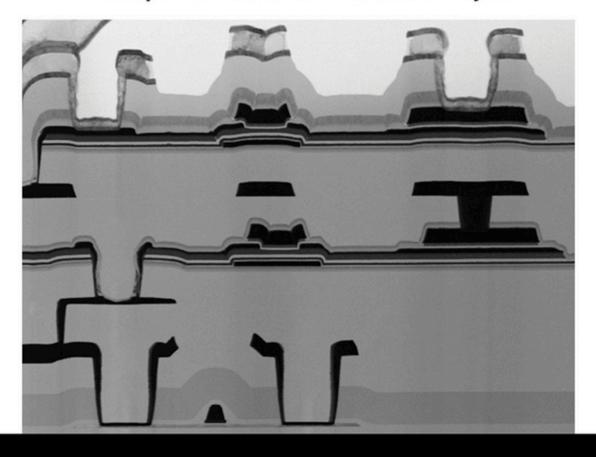

The process technology to fabricate LSI devices is introduced in Section 2.8. First, the methods used to fabricate CAAC-IGZO FETs with top-gate top-contact (TGTC) and trench-gate self-aligned (TGSA) structures are explained; then, a hybrid structure in which a CAAC-IGZO FET is placed over a Si FET is described.

### 2.2 Off-State Current

This section discusses how low the off-state current (leakage current in an off state) of the CAAC-IGZO FET is, compared with that of a conventional Si FET. A CAAC-IGZO FET has an off-state current on the order of yoctoamps ( $10^{-24}$  A), below the detection limit of common current measurement (0.1 pA). As possibilities for measuring the off-state current, methods utilizing a FET with increased channel width (*W*) and the voltage drop of a capacitor are discussed. The reason for the extremely low off-state current of the CAAC-IGZO FET is also discussed theoretically with reference to an energy band diagram.

### 2.2.1 Off-State Current Comparison between Si and CAAC-IGZO FETs

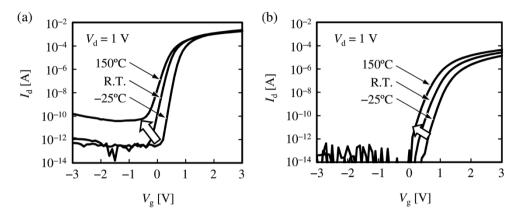

The off-state currents of Si and CAAC-IGZO FETs are compared with each other (see Figure 2.3). Their drain current–gate voltage  $(I_d-V_g)$  characteristics are obtained under  $-25^{\circ}$ C, room temperature (R.T.), and 150°C at a drain voltage  $V_d$  of 1 V. As shown in Figure 2.3(a), the off-state current of the Si FET is not lower than the detection limit of 0.1 pA  $(10^{-13} \text{ A})$ , and increases with the measurement temperature. Possible reasons for the off-state current in the Si FET are p-n junction leakage and current generated by interband thermal transition. In contrast, the CAAC-IGZO FET has an off-state current lower than the detection limit regardless of the temperature, as shown in Figure 2.3(b). Because the CAAC-IGZO FET operates in an *n*-channel accumulation mode, p-n junction leakage does not occur. In addition, CAAC-IGZO has a wide bandgap of approximately 3 eV and few mid-gap levels, so the conduction band carrier generation by interband transitions or excitations from deep levels is also negligible. The detailed mechanisms of the off-state leakage current of CAAC-IGZO FETs

are theoretically discussed in Subsection 2.2.3. Measurement methods developed to detect the yoctoamp-order off-state current of the CAAC-IGZO FET are described in Subsection 2.2.2.

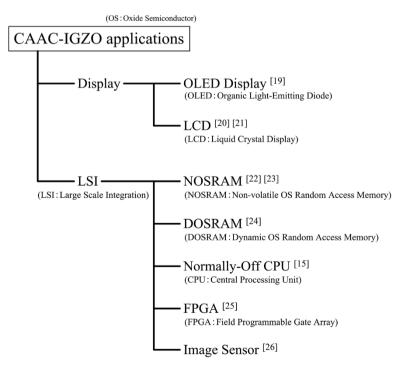

Such an extremely low off-state current, which cannot be obtained in Si FETs, leads to an ultra-low-power device. Various device applications of CAAC-IGZO FET technology have been reported (see Figure 2.4) [18].

**Figure 2.3** Comparison of off-state current between (a) Si FET with  $W/L=0.35 \,\mu\text{m}/10 \,\mu\text{m}$  and (b) CAAC-IGZO FET with  $W/L=0.45 \,\mu\text{m}/10 \,\mu\text{m}$ . *Source:* Adapted from [17]

Figure 2.4 Applications of CAAC-IGZO FET technology to various devices. *Source*: Adapted from [18]

### 2.2.2 Measurement of Extremely Low Off-State Current

The extremely low off-state current of the CAAC-IGZO FET is on the order of  $10^{-24}$  A, which is lower than the detection limit (0.1 pA) of common current measurement methods. The offstate current, flowing between a source and a drain when the FET is off, increases in proportion to the channel width. To allow an off-state current measurement, the channel width of the CAAC-IGZO FET is increased to be as wide as 1 m.

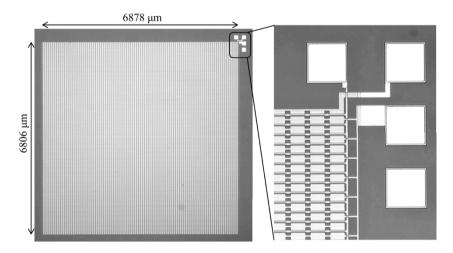

Figure 2.5 shows micrographs of a CAAC-IGZO FET with channel length L of 3  $\mu$ m and channel width W of 1 m [10]. In the left photograph, 20,000 (200 × 100) CAAC-IGZO FETs, each having  $W = 50 \mu$ m, are aligned in the 6806  $\mu$ m × 6878  $\mu$ m region. The right photograph is an enlarged view of the region enclosed in a square in the left photograph. These CAAC-IGZO FETs are parallel-connected, forming a CAAC-IGZO FET with a total channel width of 1 m.

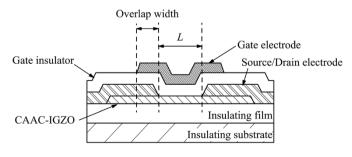

The cross-sectional structure of one CAAC-IGZO FET is shown in Figure 2.6. This FET has a TGTC structure and employs an overlap structure whereby the gate electrode overlaps with

**Figure 2.5** Micrographs of the CAAC-IGZO FET with W = 1 m. *Source*: Reproduced from [10], with permission of *Japanese Journal of Applied Physics*

Figure 2.6 Cross-sectional view of the CAAC-IGZO FET

the source and drain electrodes (the overlap width is  $2 \mu m$ ). On a glass substrate, the following films are formed in the order they are listed.

- Base insulating film: 300-nm-thick silicon oxide (amorphous)

- Active layer: 30-nm-thick CAAC-IGZO film

- Source and drain electrodes: 100-nm-thick tungsten

- · Gate insulator (sometimes referred to as GI): 100-nm-thick silicon oxide

- · Gate electrode: stack of 15-nm-thick tantalum nitride and 135-nm-thick tungsten

- Passivation layer: 300-nm-thick silicon oxide (not shown)

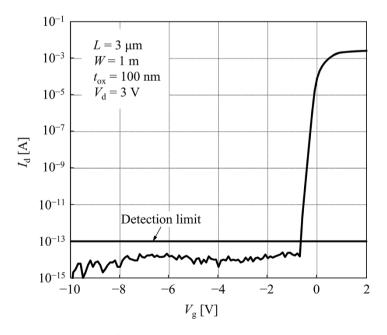

The  $I_d$ - $V_g$  characteristics of the CAAC-IGZO FET with W = 1 m at  $V_d = 3$  V are shown in Figure 2.7. For the measurement, an Agilent 4156C Precision Semiconductor Parameter Analyzer is used. According to Figure 2.7, even though the channel width is as wide as 1 m, the off-state current of the fabricated CAAC-IGZO FET is lower than the detection limit of 0.1 pA.

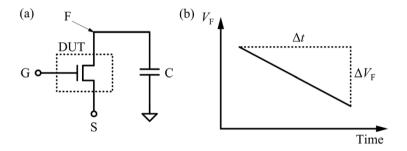

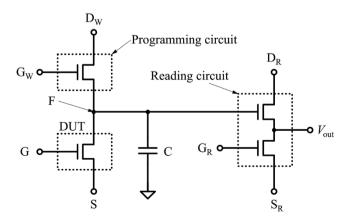

In order to obtain the off-state current, another method has therefore been developed. To measure the minute current, the small amount of charge moved by the current should be increased to a detectable level. Then, a method of estimating the current by measuring the charge in the charge over a long time is developed. Figure 2.8 shows the conceptual diagram of this measurement method. A device under test (here, a CAAC-IGZO FET), which is the element to be measured, is denoted by "DUT." Figure 2.8(a) shows a configuration used to measure the current of the DUT, and Figure 2.8(b) shows the time change of the potential

**Figure 2.7**  $I_d-V_g$  characteristics of the CAAC-IGZO FET with W = 1 m.  $T_{ox}$  denotes the thickness of the gate insulator. *Source*: Reproduced from [10], with permission of *Japanese Journal of Applied Physics*

$V_{\rm F}$  of node F connected to the DUT. The leakage current *I* of the DUT is expressed by the following equation:

$$I = \frac{C_{\rm F} \Delta V_{\rm F}}{\Delta t} \tag{2.1}$$