# **CIRCUIT SIMULATION**

# **CIRCUIT SIMULATION**

Farid N. Najm

A JOHN WILEY & SONS, INC., PUBLICATION

Copyright © 2010 by John Wiley & Sons, Inc. All rights reserved.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permission.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services or for technical support, please contact our Customer Care Department within the United States at (800) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic formats. For more information about Wiley products, visit our web site at www.wiley.com.

#### Library of Congress Cataloging-in-Publication Data:

Najm, Farid N.

Circuit simulation / Farid N. Najm.

p. cm.

Includes bibliographical references and index.

ISBN 978-0-470-53871-5

1. Electronic circuits–Computer simulation. 2. Electronic circuits–Mathematical models.

3. Integrated circuits–Computer simulation. I. Title.

TK7867.N33 2010

621.381501'13-dc22

2009022673

Printed in the United States of America.

10 9 8 7 6 5 4 3 2

To my wife, *Diana*, and to our two daughters, *Lily Marie* and *Tanya Kristen*.

## CONTENTS

| List                | t of H         | Figures                                                                                                                                                                                | xiii                             |  |

|---------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|

| List                | ist of Tables  |                                                                                                                                                                                        |                                  |  |

| Pre                 | Preface        |                                                                                                                                                                                        |                                  |  |

| 1                   | l Introduction |                                                                                                                                                                                        |                                  |  |

|                     | 1.1            | Device Equations                                                                                                                                                                       | 2                                |  |

|                     | 1.2            | Equation Formulation                                                                                                                                                                   | 3                                |  |

|                     | 1.3            | <ul><li>Solution Techniques</li><li>1.3.1 Nonlinear Circuits</li><li>1.3.2 Dynamic Circuits</li></ul>                                                                                  | 6<br>7<br>8                      |  |

|                     | 1.4            | Circuit Simulation Flow<br>1.4.1 Analysis Modes                                                                                                                                        | 8<br>9                           |  |

|                     | Not            | es                                                                                                                                                                                     | 10                               |  |

|                     | Pro            | blems                                                                                                                                                                                  | 10                               |  |

| 2 Network Equations |                | 13                                                                                                                                                                                     |                                  |  |

|                     | 2.1            | <ul><li>Elements and Networks</li><li>2.1.1 Passive Elements</li><li>2.1.2 Active Elements</li><li>2.1.3 Equivalent Circuit Model</li><li>2.1.4 Network Classification</li></ul>       | 13<br>13<br>15<br>17<br>18       |  |

|                     | 2.2            | Topological Constraints<br>2.2.1 Network Graphs                                                                                                                                        | 19<br>19                         |  |

|                     | 2.3            | <ul><li>Cycle Space and Bond Space</li><li>2.3.1 Current Assignments</li><li>2.3.2 Voltage Assignments</li><li>2.3.3 Orthogonal Spaces</li><li>2.3.4 Topological Constraints</li></ul> | 23<br>23<br>24<br>24<br>24<br>25 |  |

|   |      |          | Fundamental Circulation<br>Fundamental Potential Difference | 25<br>27 |

|---|------|----------|-------------------------------------------------------------|----------|

|   | 2.4  |          |                                                             |          |

|   | 2.4  |          | Ilation of Linear Algebraic Equations                       | 27<br>28 |

|   |      |          | Sparse Tableau Analysis<br>Nodal Analysis                   | 28<br>29 |

|   |      |          | Unique Solvability                                          | 30       |

|   |      |          | Modified Nodal Analysis                                     | 33       |

|   | 2.5  | Formu    | lation of Linear Dynamic Equations                          | 42       |

|   |      | 2.5.1    | Dynamic Element Stamps                                      | 43       |

|   |      | 2.5.2    | Unique Solvability                                          | 44       |

|   | Not  | es       |                                                             | 45       |

|   | Prol | olems    |                                                             | 45       |

| 3 | Solı | ition of | f Linear Algebraic Circuit Equations                        | 49       |

|   | 3.1  | Direct   | Methods                                                     | 50       |

|   |      | 3.1.1    | Matrix Preliminaries                                        | 50       |

|   |      | 3.1.2    | Gaussian Elimination (GE)                                   | 54       |

|   |      |          | LU Factorization                                            | 60       |

|   |      |          | Block Gaussian Elimination                                  | 71       |

|   |      | 3.1.5    | Cholesky Decomposition                                      | 73       |

|   | 3.2  | Accura   | acy and Stability of GE                                     | 74       |

|   |      | 3.2.1    | Error                                                       | 75       |

|   |      | 3.2.2    | Floating Point Numbers                                      | 78       |

|   |      | 3.2.3    | Norms                                                       | 80       |

|   |      | 3.2.4    | Stability of GE and LU Factorization                        | 83       |

|   |      | 3.2.5    | Pivoting for Accuracy                                       | 86       |

|   |      | 3.2.6    | Conditioning of $Ax = b$                                    | 89       |

|   |      | 3.2.7    | Iterative Refinement                                        | 96       |

|   | 3.3  |          | ct/Iterative Methods                                        | 97       |

|   |      |          | Gauss-Jacobi                                                | 98       |

|   |      |          | Gauss-Seidel                                                | 99       |

|   |      | 3.3.3    | Convergence                                                 | 100      |

|   | 3.4  |          | oning Techniques                                            | 104      |

|   |      | 3.4.1    | Node Tearing                                                | 104      |

|   |      | 3.4.2    | Direct Methods                                              | 106      |

|   |      | 3.4.3    | Indirect Methods                                            | 107      |

|   | 3.5  | Sparse   | e Matrix Techniques                       | 109 |

|---|------|----------|-------------------------------------------|-----|

|   |      | 3.5.1    | Sparse Matrix Storage                     | 110 |

|   |      | 3.5.2    | Sparse GE and LU Factorization            | 112 |

|   |      | 3.5.3    | Reordering and Sparsity                   | 113 |

|   |      | 3.5.4    | Pivoting for Sparsity                     | 115 |

|   |      | 3.5.5    | Markowitz Pivoting                        | 116 |

|   |      | 3.5.6    | Diagonal Pivoting                         | 119 |

|   |      | 3.5.7    | The Symmetric (SPD) Case                  | 120 |

|   |      | 3.5.8    | Extension to the Non-SPD Case             | 122 |

|   | Not  | es       |                                           | 125 |

|   | Prol | olems    |                                           | 125 |

| 4 | Solu | ution of | f Nonlinear Algebraic Circuit Equations   | 127 |

|   | 4.1  | Nonlin   | near Network Equations                    | 127 |

|   |      | 4.1.1    | Nonlinear Elements                        | 128 |

|   |      | 4.1.2    | Nonlinear MNA Formulation                 | 129 |

|   |      | 4.1.3    | Preparing for a DC Analysis               | 133 |

|   | 4.2  | Solutio  | on Techniques                             | 133 |

|   |      | 4.2.1    | Iterative Methods and Convergence         | 134 |

|   |      | 4.2.2    | Introduction to Newton's Method           | 136 |

|   |      | 4.2.3    | The One-Dimensional Case                  | 139 |

|   |      | 4.2.4    | The Multidimensional Case                 | 148 |

|   |      | 4.2.5    | Quasi-Newton Methods                      | 152 |

|   | 4.3  | Applic   | eation to Circuit Simulation              | 154 |

|   |      | 4.3.1    | Linearization and Companion Models        | 154 |

|   |      | 4.3.2    | Some Test Cases                           | 156 |

|   |      | 4.3.3    | Generalization                            | 162 |

|   |      | 4.3.4    | Considerations for Multiterminal Elements | 166 |

|   |      | 4.3.5    | Multivariable Differentiation             | 167 |

|   |      | 4.3.6    | Linearization of Multiterminal Elements   | 171 |

|   |      | 4.3.7    | Elements with Internal Nodes              | 176 |

|   | 4.4  | •        | Newton Methods in Simulation              | 181 |

|   |      | 4.4.1    | Damping Methods                           | 182 |

|   |      | 4.4.2    | Overview of More General Methods          | 186 |

|   |      | 4.4.3    | Source Stepping                           | 187 |

|   |      | 4.4.4    | Gmin Stepping                             | 189 |

|   |      |          |                                           |     |

|   |      | 4.4.5    | Pseudo-Transient                      | 189 |

|---|------|----------|---------------------------------------|-----|

|   |      | 4.4.6    | Justification for Pseudo-Transient    | 193 |

|   | Not  | es       |                                       | 196 |

|   | Prol | blems    |                                       | 197 |

| 5 | Solu | ution of | f Differential Circuit Equations      | 201 |

|   | 5.1  | Differ   | ential Network Equations              | 201 |

|   |      | 5.1.1    | Dynamic Elements                      | 201 |

|   |      | 5.1.2    | Dynamic MNA Equations                 | 203 |

|   |      | 5.1.3    | DAEs and ODEs                         | 204 |

|   | 5.2  | ODE S    | Solution Techniques                   | 206 |

|   |      | 5.2.1    | ODE Systems and Basic Theorems        | 206 |

|   |      | 5.2.2    | Overview of Solution Methods          | 209 |

|   |      | 5.2.3    | Three Basic Methods: FE, BE, and TR   | 211 |

|   |      | 5.2.4    | Quality Metrics                       | 215 |

|   |      | 5.2.5    | Linear Multistep Methods              | 220 |

|   | 5.3  | Accur    | acy of LMS Methods                    | 221 |

|   |      | 5.3.1    | Order                                 | 221 |

|   |      | 5.3.2    | Consistency                           | 223 |

|   |      | 5.3.3    | The Backward Differentiation Formulas | 224 |

|   |      | 5.3.4    | Local Truncation Error                | 225 |

|   |      | 5.3.5    | Deriving the LMS Methods              | 228 |

|   |      | 5.3.6    | Solving Implicit Methods              | 229 |

|   |      | 5.3.7    | Interpolation Polynomial              | 231 |

|   |      | 5.3.8    | Estimating the LTE                    | 237 |

|   | 5.4  | Stabili  | ity of LMS Methods                    | 241 |

|   |      | 5.4.1    | Linear Stability Theory               | 242 |

|   |      | 5.4.2    | The Test Equation                     | 243 |

|   |      | 5.4.3    | Absolute Stability                    | 246 |

|   |      | 5.4.4    | Stiff Systems                         | 252 |

|   |      | 5.4.5    | Stiff Stability                       | 253 |

|   |      | 5.4.6    | Remarks                               | 256 |

|   | 5.5  | Trapez   | zoidal Ringing                        | 257 |

|   |      | 5.5.1    | Smoothing                             | 258 |

|   |      | 5.5.2    | Extrapolation                         | 259 |

|   | 5.6  | Variab   | ble Time-Step Methods                 | 261 |

|              | 5.6.1  | Implementing a Change of Time-Step          | 262 |

|--------------|--------|---------------------------------------------|-----|

|              | 5.6.2  | Interpolation Methods                       | 262 |

|              | 5.6.3  | Variable-Coefficient Methods                | 264 |

|              | 5.6.4  | Variable Step Variable Order (VSVO) Methods | 265 |

| 5.7          | Applic | ation to Circuit Simulation                 | 265 |

|              | 5.7.1  | From DAEs to Algebraic Equations            | 266 |

|              | 5.7.2  | FE Discretization                           | 269 |

|              | 5.7.3  | BE Discretization                           | 271 |

|              | 5.7.4  | TR Discretization                           | 277 |

|              | 5.7.5  | Charge-Based and Flux-Based Models          | 282 |

|              | 5.7.6  | Multiterminal Elements                      | 291 |

|              | 5.7.7  | Time-Step Control                           | 296 |

|              | 5.7.8  | Enhancements                                | 298 |

|              | 5.7.9  | Overall Flow                                | 299 |

| Notes        | 8      |                                             | 300 |

| Probl        | ems    |                                             | 300 |

| Glossary     |        |                                             | 305 |

| Bibliography |        |                                             | 307 |

| Index        |        |                                             | 311 |

## LIST OF FIGURES

| 1.1  | A resistor.                                                                                                                                         | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | A capacitor.                                                                                                                                        | 3  |

| 1.3  | Nonlinear resistor.                                                                                                                                 | 3  |

| 1.4  | A simple linear circuit.                                                                                                                            | 4  |

| 1.5  | A linear circuit, used to demonstrate the MNA formulation.                                                                                          | 6  |

| 1.6  | An $i$ - $v$ characteristic for a nonlinear resistor, showing linearization around a candidate solution point.                                      | 7  |

| 1.7  | A linear circuit that has the same current-voltage characteristic as the tangent line in Fig. 1.6.                                                  | 8  |

| 1.8  | Overall circuit simulation flow.                                                                                                                    | 9  |

| 2.1  | The symbols for (a) a linear resistor and (b) a nonlinear resistor.                                                                                 | 14 |

| 2.2  | The symbol for a capacitor (a) and an illustrative plot of capacitance<br>as a function of voltage (b) for a nonlinear capacitor.                   | 14 |

| 2.3  | The symbol for an inductor (a) and an illustrative plot of inductance<br>as a function of current (b) for a nonlinear inductor.                     | 15 |

| 2.4  | Symbols for (a) a constant independent voltage source, (b) a time-<br>varying independent voltage source, and (c) an independent current<br>source. | 15 |

| 2.5  | Controlled voltage sources, showing a linear voltage-controlled source (a) and a linear current-controlled source (b).                              | 16 |

| 2.6  | Controlled current sources, showing a linear voltage-controlled source (a) and a linear current-controlled source (b).                              | 16 |

| 2.7  | Replacement of a nonlinear VCVS by an equivalent circuit containing only <i>linear</i> controlled sources.                                          | 16 |

| 2.8  | The pn-junction diode, showing its structure, circuit symbol, and current-voltage characteristic.                                                   | 17 |

| 2.9  | An equivalent circuit model for a diode.                                                                                                            | 18 |

| 2.10 | The n-channel MOSFET, showing its structure, circuit symbol, and<br>a simple version of its equivalent circuit model.                               | 18 |

| 2.11 | A circuit element and the corresponding graph edge.                                                                                                 | 19 |

| 2.12 | A circuit, its directed graph, and its undirected graph.                                                                                            | 20 |

|      |                                                                                                                                                     |    |

| 2.13 | Edge labels, shown on a directed and an undirected graph.                                                  | 20 |

|------|------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Cycles in a graph, corresponding to edges that are not part of the chosen spanning tree.                   | 26 |

| 2.15 | A resistor.                                                                                                | 36 |

| 2.16 | Element stamp for a resistor in group 1.                                                                   | 36 |

| 2.17 | Element stamp for a resistor in group 2.                                                                   | 36 |

| 2.18 | An independent current source.                                                                             | 37 |

| 2.19 | Element stamp for an independent current source in group 1.                                                | 37 |

| 2.20 | Element stamp for an independent current source in group 2.                                                | 37 |

| 2.21 | An independent voltage source.                                                                             | 38 |

| 2.22 | Element stamp for an independent voltage source.                                                           | 38 |

| 2.23 | A voltage-controlled voltage source.                                                                       | 39 |

| 2.24 | Element stamp for a VCVS.                                                                                  | 39 |

| 2.25 | A current-controlled voltage source.                                                                       | 40 |

| 2.26 | Element stamp for a CCVS.                                                                                  | 40 |

| 2.27 | A circuit to demonstrate the MNA equation formulation.                                                     | 40 |

| 2.28 | A capacitor.                                                                                               | 43 |

| 2.29 | Element stamp for a capacitor in group 1.                                                                  | 43 |

| 2.30 | Element stamp for a capacitor in group 2.                                                                  | 44 |

| 2.31 | An inductor.                                                                                               | 44 |

| 2.32 | Element stamp for an inductor.                                                                             | 44 |

| 2.33 | Linear network for problem 2.1.                                                                            | 45 |

| 2.34 | A test circuit.                                                                                            | 46 |

| 2.35 | Circuit description file for the circuit in Fig. 2.34.                                                     | 47 |

| 3.1  | The core of a Gaussian elimination algorithm.                                                              | 56 |

| 3.2  | An implementation of forward substitution that is appropriate when a matrix is stored <i>by rows</i> .     | 62 |

| 3.3  | An implementation of forward substitution that is appropriate when a matrix is stored <i>by columns</i> .  | 62 |

| 3.4  | An implementation of backward substitution that is appropriate when a matrix is stored <i>by rows</i> .    | 63 |

| 3.5  | An implementation of backward substitution that is appropriate when a matrix is stored <i>by columns</i> . | 63 |

| 3.6  | Crout's algorithm for LU factorization.                                                                    | 66 |

| 3.7  | Doolittle's algorithm for LU factorization.                                                                | 67 |

| 3.8  | Gauss's algorithm for LU factorization.                                                                    | 70 |

| 3.9  | Cholesky decomposition for LU factorization, where $U = L^{T}$ .                                           | 74 |

| 3.10 | Illustration of relations among the various error terms, including forward and backward error.                   | 77  |

|------|------------------------------------------------------------------------------------------------------------------|-----|

| 3.11 | The geometric interpretation of ill-conditioning, in the case of a two-dimensional system [after Ruehli (1986)]. | 91  |

| 3.12 | Iterative refinement algorithm.                                                                                  | 96  |

| 3.13 | The Gauss-Jacobi algorithm.                                                                                      | 99  |

| 3.14 | The Gauss-Seidel algorithm.                                                                                      | 100 |

| 3.15 | An illustration of node tearing, where a circuit is partitioned into four sub-circuits.                          | 105 |

| 4.1  | An equivalent circuit for a nonlinear VCVS, $v_e = f(v_x)$ , using <i>linear</i> controlled sources.             | 128 |

| 4.2  | A nonlinear circuit used to illustrate equation formulation.                                                     | 131 |

| 4.3  | Newton's method.                                                                                                 | 137 |

| 4.4  | A graphical illustration of Newton's method in one dimension.                                                    | 141 |

| 4.5  | Oscillation in Newton's method.                                                                                  | 143 |

| 4.6  | Divergence in Newton's method.                                                                                   | 144 |

| 4.7  | A graphical illustration of the secant method.                                                                   | 145 |

| 4.8  | A graphical illustration of the Newton-chord method.                                                             | 145 |

| 4.9  | Existence of a fixed point [after Burden and Faires (2005)].                                                     | 146 |

| 4.10 | The fixed point algorithm.                                                                                       | 147 |

| 4.11 | Illustration of progress of the fixed point method [after Chua and Lin (1975)].                                  | 147 |

| 4.12 | A diode.                                                                                                         | 155 |

| 4.13 | Companion model for a diode.                                                                                     | 156 |

| 4.14 | A simple diode circuit.                                                                                          | 157 |

| 4.15 | A linear circuit replacement that provides the solution for the $k$ -th Newton iteration.                        | 158 |

| 4.16 | Another diode circuit.                                                                                           | 161 |

| 4.17 | A linearization of the circuit in Fig. 4.16, using the diode companion model.                                    | 162 |

| 4.18 | A general multiterminal element.                                                                                 | 166 |

| 4.19 | An equivalent circuit for a general multiterminal element.                                                       | 167 |

| 4.20 | The Ebers-Moll model for an npn BJT.                                                                             | 172 |

| 4.21 | A companion model for the npn BJT.                                                                               | 174 |

| 4.22 | An n-channel MOSFET.                                                                                             | 175 |

| 4.23 | A simple companion model for the n-channel MOSFET.                                                               | 176 |

| 4.24 | More detailed companion models for the BJT and the MOSFET, including series resistance and internal nodes.       | 177 |

| 4.25 | A diode with series resistance and its companion model.                                                                   | 177 |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

| 4.26 | A transformed companion model for the diode, in which the internal node has been eliminated.                              | 178 |

| 4.27 | A diode with series resistance, biased in the standard bias arrangement for multiterminal elements.                       | 180 |

| 4.28 | Source transformations for pseudo-transient.                                                                              | 192 |

| 4.29 | Voltage source transformation for pseudo-transient.                                                                       | 194 |

| 4.30 | Current source transformation for pseudo-transient.                                                                       | 195 |

| 4.31 | A nonlinear test circuit.                                                                                                 | 199 |

| 4.32 | Solution of problem 4.8.                                                                                                  | 199 |

| 5.1  | The region of absolute stability in the $h\lambda$ -plane maps to the interior of the unit circle in the <i>r</i> -plane. | 247 |

| 5.2  | The region of absolute stability for FE.                                                                                  | 249 |

| 5.3  | The region of absolute stability for BE.                                                                                  | 250 |

| 5.4  | The region of absolute stability for TR.                                                                                  | 252 |

| 5.5  | The shaded region must be part of the region of absolute stability for any stiffly stable system.                         | 254 |

| 5.6  | The region of absolute stability for BDF2.                                                                                | 254 |

| 5.7  | The region of absolute stability for the 3rd order BDF.                                                                   | 254 |

| 5.8  | The region of absolute stability for the 4th order BDF.                                                                   | 255 |

| 5.9  | The region of absolute stability for the 5th order BDF.                                                                   | 255 |

| 5.10 | The region of absolute stability for the 6th order BDF.                                                                   | 255 |

| 5.11 | Typical trapezoidal ringing, from simulation.                                                                             | 258 |

| 5.12 | Companion models for the case of FE.                                                                                      | 270 |

| 5.13 | Companion models for linear $L$ and $C$ , for the case of BE.                                                             | 273 |

| 5.14 | Companion models for nonlinear $L$ and $C$ , for the case of BE.                                                          | 275 |

| 5.15 | TR companion models for linear elements.                                                                                  | 279 |

| 5.16 | TR companion models for nonlinear elements.                                                                               | 280 |

| 5.17 | A nonlinear RC circuit.                                                                                                   | 281 |

| 5.18 | The circuit of Fig. 5.17, using companion models to find the solution at time $t_{n+1}$ .                                 | 281 |

| 5.19 | The circuit of Fig. 5.18, after replacement of the nonlinear controlled source by its linearized companion model.         | 281 |

| 5.20 | Overall solution flow.                                                                                                    | 282 |

| 5.21 | A simple test circuit.                                                                                                    | 285 |

| 5.22 | An RC circuit with a nonlinear capacitor.                  | 287 |

|------|------------------------------------------------------------|-----|

| 5.23 | A general template for multiterminal elements.             | 291 |

| 5.24 | An equivalent circuit for a general multiterminal element. | 292 |

| 5.25 | Overall simulation flow.                                   | 299 |

| 5.26 | A test circuit for time-domain simulation.                 | 302 |

| 5.27 | The solution for the circuit in Fig. 5.26.                 | 303 |

## LIST OF TABLES

| 2.1 | Element stamp for a resistor in group 1.                                               | 36  |

|-----|----------------------------------------------------------------------------------------|-----|

| 2.2 | Element stamp for a resistor in group 2.                                               | 37  |

| 2.3 | Element stamp for an independent current source in group 1.                            | 38  |

| 2.4 | Element stamp for an independent current source in group 2.                            | 38  |

| 2.5 | Element stamp for an independent voltage source.                                       | 39  |

| 2.6 | Element stamp for a VCVS.                                                              | 39  |

| 2.7 | Element stamp for a CCVS.                                                              | 40  |

| 2.8 | Element stamps for elements $e_1$ and $e_2$ in the circuit shown in Fig. 2.27.         | 41  |

| 2.9 | Element stamps for elements $e_3$ and $e_4$ in the circuit shown in Fig. 2.27.         | 41  |

| 4.1 | A comparison of linear and quadratic convergence rates.                                | 136 |

| 5.1 | Error constants for the BDFs.                                                          | 256 |

| 5.2 | Element stamp for a capacitor, based on FE discretization and linearization.           | 271 |

| 5.3 | Element stamp for an inductor, based on FE discretization and linearization.           | 271 |

| 5.4 | Element stamp for a linear capacitor, based on BE discretization and linearization.    | 274 |

| 5.5 | Element stamp for a linear inductor, based on BE discretization and linearization.     | 275 |

| 5.6 | Element stamp for a nonlinear capacitor, based on BE discretization and linearization. | 276 |

This text describes in detail the numerical techniques and algorithms that are part of modern circuit simulators, with a focus on the most commonly used simulation modes: DC Analysis and Transient Analysis. After a general introduction in chapter 1, network equation formulation is covered in chapter 2, with emphasis on modified nodal analysis (MNA). The coverage also includes the network cycle space and bond space, element stamps, and the question of unique solvability of the system. Solving linear resistive circuits is the focus of chapter 3, which gives a comprehensive treatment of the most relevant aspects of linear system solution techniques. This includes the standard methods of Gaussian elimination (GE) and LU factorization, as well as some in-depth treatment of numerical error in floating point systems, pivoting for accuracy, sparse matrix methods, and pivoting for sparsity. Indirect solution methods, such as Gauss-Jacobi (GJ) and Gauss-Seidel (GS) are also covered. As well, some discussion of node tearing and partitioning is given, in recognition of the recent trend of increased usage of parallel software on multi-core computers.

Solving nonlinear resistive circuits is covered in chapter 4, with a focus on Newton's method. A detailed study is given of Newton's method, including its links to the fixed point method and the conditions that govern its convergence. A rigorous treatment is then provided of how this method applies to circuit simulation, leading up to the notion of companion models for nonlinear resistive elements, with coverage of multiterminal elements. As well, a coverage of quasi-Newton methods in simulation is provided, which includes the three commonly used homotopy methods for DC Analysis: source stepping, Gmin stepping, and pseudo-transient. Simulation of dynamic circuits, both linear and nonlinear, is covered in chapter 5. This chapter gives a detailed treatment of methods for solving ordinary differential equations (ODEs), with a focus on those methods that have been found useful for circuit simulation. Issues of accuracy and stability of linear multistep methods are covered in some depth. These methods are then applied to circuit simulation, illustrating how the companion models of dynamic elements are derived. Here too, multiterminal elements are addressed, as well as other advanced topics of time-step control, variable time-step, charge conservation, and the use of charge-based models in simulation.

My aim throughout has been to produce a text that has two key features: 1) sufficient depth and breadth so that it can be used in a graduate course on the topic, and 2) enough detail so as to allow the reader to write his/her own basic circuit simulator. I hope that I have succeeded. Indeed, the book has already

been tested for this dual purpose, as I have used it to teach a graduate course on circuit simulation at the University of Toronto. As part of this course, students write a rudimentary circuit simulator, in a sequence of five computer projects, all of which are included in the problem sets in this text. The first project is simply to develop a parser; the second is to develop code that builds the MNA system of equations for any linear resistive circuit, using element stamps; the third requires the implementation of an LU factorization capability to solve the MNA system. The fourth project implements a Newton loop around the MNA solver, allowing the simulation of basic nonlinear resistive circuits. The fifth and final project builds a time-domain simulation loop around the Newton loop, using the trapezoidal rule. The result is a basic simulator that can simulate circuits containing MOSFETs, BJTs, and diodes (using the simplest first-order models for these devices), along with the standard linear elements. With problem sets and computer projects at the end of every chapter, this text is suitable as the main textbook for a course on the topic. As well, the text has sufficient depth that I hope it would serve as a reference for practicing design engineers and computer-aided design practitioners.

Throughout the text, detailed coverage is given of the mathematical and numerical techniques that are the basis for the various simulation topics. Such a theoretical background is important, I feel, for a full understanding of the practical simulation techniques. However, this theoretical background is given piecemeal, as the need arises, and is never presented as an end in itself; it is scattered throughout the text and paired up with the various simulation topics. Furthermore, and in order to maintain the focus on the end-goal of practical simulation methods, I have found it necessary to *state all theorems without proof*. Ample references are provided, however, which the interested reader can consult for a deeper study.

Finally, the reader is encouraged to consult the following web site, where I hope to maintain various resources that are relevant to this book, including an up-to-date list of any known errors:

```

http://www.eecg.utoronto.ca/~najm/simbook

```

#### ACKNOWLEDGMENTS

I owe much gratitude to Professors Ibrahim N. Hajj and Vasant B. Rao, then at the University of Illinois, who taught me much of what I know about circuit simulation. Ibrahim was also kind enough to provide his extensive set of notes on the topic, which were very helpful as, many years later, I contemplated teaching a course on this topic. It has taken a lot more reading and discussions with many other colleagues to help bring this book project to fruition. I would especially like to thank my friends from the Texas Instruments circuit simulation group, Lawrence A. Arledge and David C. Yeh, for extensive discussions over the last two years. Thanks as well to my friend John F. Croix for answering my many questions on time-step control and transient simulation. Thanks to my graduate students, Khaled R. Heloue, Nahi H. Abdul Ghani, and Sari Onaissi, for their help in proof-reading parts of the manuscript and in helping to develop the computer projects. Last but not least, I owe a big *thank you* to my wife, Diana Tawil Najm, for her patience over the last two years, during which I was virtually "absent" as I repeatedly revised the manuscript. Without her support, this would not have been possible.

Farid N. Najm January 2010 Toronto, Canada

# Introduction

Circuit simulation is a technique for checking and verifying the design of electrical and electronic circuits and systems prior to manufacturing and deployment. It is used across a wide spectrum of applications, ranging from integrated circuits and microelectronics to electrical power distribution networks and power electronics. Circuit simulation is a mature and established art and also remains an important area of research. This text covers the theoretical background for circuit simulation, as well as the numerical techniques that are at the core of modern circuit simulators. Circuit simulation combines a) mathematical modeling of the circuit *elements*, or *devices*, b) formulation of the circuit/network equations, and c) techniques for solution of these equations. We will focus mainly on the formulation and solution of the network equations and will not cover device modeling in any detail.

Compared to simulators that operate on a design description at higher levels of abstraction, such as logic or functional simulators, circuit simulators use a detailed (so-called circuit level or transistor level) description of the circuit and perform a relatively *accurate* simulation. Typically, such a simulation uses physical models of the circuit elements, solves the resulting differential and algebraic equations, and generates time-waveforms of node voltages and element currents. In general, a circuit simulator allows the use of any simulation primitive, provided it can be described with an appropriate device model. In practice, while some devices (e.g., resistors, capacitors) are two-terminal elements, others (e.g., transistors) have more than two terminals. However, a multiterminal element is usually modeled as a subcircuit consisting of only two-terminal elements. Thus, a common starting point for studying circuit simulation is to restrict the formulation to two-terminal elements. For integrated circuits, circuit simulators often work with an *extracted* circuit description, which gives better accuracy. Thus circuit capacitance, resistance, and inductance can be included in the analysis, be they prespecified discrete components or parasitic.

Early techniques for circuit simulation using computers were introduced in the 1950s and 1960s, and several limited-scope simulators were developed. The first general-purpose circuit simulator to experience widespread usage was SPICE, developed by L. W. Nagel at the University of California, Berkeley, in the

Circuit Simulation, by Farid N. Najm

Copyright © 2010 John Wiley & Sons, Inc.

early 1970s, under the supervision of Professor D. O. Pederson. According to Nagel (1975), SPICE evolved from an earlier simulator called CANCER that, in turn, "*emerged from a series of courses that were instructed by Professor R. A. Rohrer*" at Berkeley. The original CANCER program, described in Nagel and Rohrer (1971), was followed up by SPICE, described in Nagel and Pederson (1973), and then SPICE2, which is described in Nagel's 1975 thesis. The rest, as they say, is history, as SPICE has become the *de facto* standard circuit simulator. At the time of this writing, SPICE3f is the latest version of the program. Further information on SPICE and its history is available in Kundert (1995), in Vladimirescu (1994), and in Pederson (1984).

SPICE was developed specifically with integrated circuits in mind. Indeed, the acronym stands for *Simulation Program with Integrated Circuit Emphasis*. This, coinciding with the birth and growth of the integrated circuits industry in the 1970s, led to widespread adoption of the program. Furthermore, the availability of the SPICE code and documentation from Berkeley, for a nominal fee, spurred the development of similar circuit simulators elsewhere. Today, there are thousands of copies of circuit simulators in use across the industry, and there are many SPICE-like simulators in the market. Some semiconductor companies average over 1 million circuit simulation runs per week!

Circuit simulation issues to be covered in this book include a) device equations, b) equation formulation, and c) solution techniques. In this chapter, we will briefly introduce each of these issues and then present the overall structure of a circuit simulator.

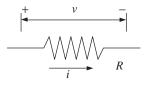

#### 1.1 DEVICE EQUATIONS

In this context, a *device* is any simulation *primitive*, or *element*, described by means of a current-voltage relationship. Thus, a resistor is described by the (Ohm's law) equation v = Ri. By convention, the positive (reference) direction for current is determined from the positive (reference) direction for voltage, as shown in Fig. 1.1, so that current flows in the device from the positive reference node to the negative node.

When the element equation contains no terms with powers of 2 or higher, the element is said to be a *linear element*. A network of linear elements is said to be a *linear circuit*. The resistor element equation is algebraic. On the other hand, a capacitor is described by i = Cdv/dt, which is a *first-order ordinary differential*

Figure 1.1: A resistor.

Figure 1.2: A capacitor.

Figure 1.3: Nonlinear resistor.

*equation*. It is first order because it contains only first-order derivatives and it is ordinary because it contains no partial derivatives. Since there are no powers of 2 or more, this too is a linear equation. Here too, the reference direction for current is based on the reference direction for voltage, as in Fig. 1.2.

Wiring is typically modeled using lumped R, L, or C elements, so that metal interconnect is described by a system of *linear first-order differential equations*. Resistors and capacitors are examples of *two-terminal* linear devices. In general, a two-terminal device may be described by an *i*-v equation i = f(v), where f can be any function  $f : \mathbb{R} \to \mathbb{R}$ . When f is a nonlinear function, the device is said to be *nonlinear* and is given the (nonlinear resistor) symbol shown in Fig. 1.3.

A pn-junction diode is an example of a commonly used two-terminal nonlinear device. Transistors, such as BJTs and MOSFETs are three-terminal nonlinear devices (four-terminal, if a detailed model is used that includes the body voltage).

#### **1.2 EQUATION FORMULATION**

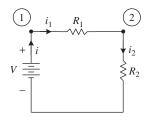

The behavior of a circuit is captured by a set of equations that are formulated by combining the element equations and Kirchoff's Current and Voltage Laws (KCL and KVL). In general, this results in a set of simultaneous *nonlinear first-order differential equations*. For a purely *resistive*, *linear*, circuit, the equations are simply a system of simultaneous linear algebraic equations.

As an example, consider the linear circuit shown in Fig. 1.4. From KCL, we can write:

$$i = i_1 = i_2$$

(1.1)

Figure 1.4: A simple linear circuit.

The element equations provide:

$$v_1 = V, \quad i_1 = \frac{v_1 - v_2}{R_1}, \quad i_2 = \frac{v_2}{R_2}$$

(1.2)

which, substituted into KCL ( $i_1 = i_2$ ), gives:

$$\frac{1}{R_1}(v_1 - v_2) = \frac{1}{R_2}v_2 \tag{1.3}$$

KVL around the loop then provides:

$$V = R_1 i_1 + R_2 i_2 = (R_1 + R_2)i = (R_1 + R_2)\frac{v_2}{R_2}$$

(1.4)

where, in the last step, we have benefited from KCL ( $i = i_2$ ) and the element equation  $i_2 = v_2/R_2$ , and this then leads to:

$$v_2 = \frac{R_2}{R_1 + R_2} V \tag{1.5}$$

With  $v_2$  in hand then, using (1.3), we get the value of  $v_1$ , and the element equation  $i_2 = v_2/R_2$  can then be used to solve for  $i = i_1 = i_2$ .

The above *ad hoc* approach of solving equations by substitution and similar operations does not scale well to large circuits. Instead, we need a *systematic* and *automatic* approach for formulating and solving the circuit equations. For now, we maintain our focus on the simple case of linear resistive circuits. There are two popular approaches for systematic equation formulation, *sparse tableau analysis* (STA) and *modified nodal analysis* (MNA). Sparse tableau analysis, described in Hachtel et al. (1971), involves the following steps:

- 1. Write KCL as Ai = 0, where A is a *reduced incidence matrix* that we will introduce later on, and *i* is a vector of all branch currents.

- 2. Write KVL as  $u = A^T v$ , where u is a vector of all branch voltages and v a vector of all nodal voltages to ground.

- 3. Write the element equations as Zi + Yu = s, where Z and Y are matrices and s is a vector.

The combination of these three sets of linear algebraic equations leads to the sparse tableau system:

$$\begin{bmatrix} A & 0 & 0 \\ 0 & I & -A^T \\ Z & Y & 0 \end{bmatrix} \begin{bmatrix} i \\ u \\ v \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ s \end{bmatrix}$$

(1.6)

This formulation has some key features in that it can be applied to *any* circuit in a systematic fashion, the equations can be assembled *directly* from the input (circuit specification), as we will see later on, and the coefficients matrix is *very* sparse (has mostly zero elements), although it is larger in dimension than the MNA matrix. Modified nodal analysis, described in Ho et al. (1975), involves the following steps:

- 1. Write KCL as Ai = 0.

- 2. Use the element equations to eliminate as many current variables as possible from KCL, leading to equations in terms of mostly branch voltages.

- 3. Use KVL to replace all the branch voltages by nodal voltages to ground.

- 4. Append element equations of those elements whose current variables could not be eliminated as additional equations of the MNA system.

We will see the details of this process later on, and it leads to the MNA system:

$$\begin{bmatrix} Y & B \\ C & Z \end{bmatrix} \begin{bmatrix} v \\ i \end{bmatrix} = \begin{bmatrix} s_v \\ s_i \end{bmatrix}$$

(1.7)

As with STA, this formulation can be applied to *any* circuit in a systematic fashion and the equations can be assembled *directly* from the input (circuit specification). As well, the coefficient matrix is sparse, but often not as sparse as the STA matrix, although it is smaller in dimension. The MNA matrix can become singular during the numerical solution process and, therefore, requires careful pivoting.

With the larger matrix size, STA can take longer to formulate the equations than MNA, but it solves them faster; it is well suited for repeated use as in statistical analysis. Most modern circuit simulators use the MNA approach.

As an example of the MNA formulation, consider the linear resistive circuit in Fig. 1.5. We write KCL at every node and then eliminate the current variables using the element equations, as follows:

KCL at node 2:

$$\frac{V - v_2}{R_1} = \frac{v_2 - v_3}{R_2} \implies \left(\frac{1}{R_1} + \frac{1}{R_2}\right)v_2 - \frac{1}{R_2}v_3 = \frac{V}{R_1}$$

KCL at node 3:  $\frac{v_2 - v_3}{R_2} = \frac{v_3}{R_3} \implies -\frac{1}{R_2}v_2 + \left(\frac{1}{R_2} + \frac{1}{R_3}\right)v_3 = 0$

Figure 1.5: A linear circuit, used to demonstrate the MNA formulation.

This leads to the MNA matrix equation:

$$\begin{bmatrix} \left(\frac{1}{R_1} + \frac{1}{R_2}\right) & \frac{-1}{R_2} \\ \frac{-1}{R_2} & \left(\frac{1}{R_2} + \frac{1}{R_3}\right) \end{bmatrix} \begin{bmatrix} v_2 \\ v_3 \end{bmatrix} = \begin{bmatrix} \frac{V}{R_1} \\ 0 \end{bmatrix}$$

(1.8)

Notice that the system matrix can be written as the sum of three matrices:

$$\begin{bmatrix} \left(\frac{1}{R_1} + \frac{1}{R_2}\right) & \frac{-1}{R_2} \\ \frac{-1}{R_2} & \left(\frac{1}{R_2} + \frac{1}{R_3}\right) \end{bmatrix} = \begin{bmatrix} \frac{1}{R_1} & 0 \\ 0 & 0 \end{bmatrix} + \begin{bmatrix} \frac{1}{R_2} & \frac{-1}{R_2} \\ \frac{-1}{R_2} & \frac{1}{R_2} \end{bmatrix} + \begin{bmatrix} 0 & 0 \\ 0 & \frac{1}{R_3} \end{bmatrix}$$

(1.9)

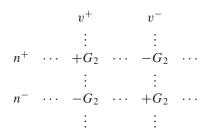

each of which relates to a specific element. These contributions of the various elements are called *element stamps*, as we will see later on. In general, a resistor like  $R_2$ , which is not connected to ground, has the following element stamp:

where  $G_2 = 1/R_2$ . This and similar element stamps are used to directly build the required MNA matrix as the simulator is reading (parsing) the circuit description file.

#### **1.3 SOLUTION TECHNIQUES**

As seen in the above examples, such as in (1.8), solving linear resistive circuits reduces to solving the *linear system*:

$$Ax = b \tag{1.10}$$

This is a classical problem that is basic to many engineering disciplines and has a variety of solution techniques. Direct methods of solution include matrix inversion, Gaussian elimination, and LU factorization. Indirect methods (relaxation methods) of solution include Gauss-Jacobi and Gauss-Seidel, successive over-relaxation, etc. The most common method is LU factorization, which proceeds as follows:

- 1. Factor A as A = LU, where L is lower-diagonal and U is upper-diagonal.

- 2. Solve Lz = b for z, by forward substitution.

- 3. Solve Ux = z for x, by backward substitution.

We will see the details of this process later on and we will recognize that a most desirable property throughout all this is *matrix sparsity*.

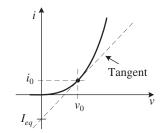

#### 1.3.1 Nonlinear Circuits

Solving nonlinear circuits is typically done using *Newton's method*. We will see that this means that we repeatedly, until convergence, perform the following two steps:

- 1. Linearize the circuit equations around a candidate solution point.

- 2. *Solve* the resulting linear circuit using *LU* factorization to discover a better solution point.

In this way, the MNA formulation for linear resistive circuits turns out to be *suf-ficient*, because the solution of a nonlinear circuit is reduced to repeated solutions of linearized versions of that circuit.

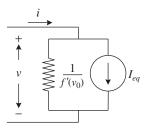

As an example of the process of linearization around a candidate solution point, consider a nonlinear resistor with the element equation i = f(v), as depicted in Fig. 1.6. The equation of the tangent line at the point  $(v_0, i_0)$  is:

$$i = f'(v_0) [v - v_0] + i_0 = f'(v_0)v + I_{eq}$$

(1.11)

**Figure 1.6:** An *i*-*v* characteristic for a nonlinear resistor, showing linearization around a candidate solution point.

**Figure 1.7:** A linear circuit that has the same current–voltage characteristic as the tangent line in Fig. 1.6.

where  $I_{eq} = i_0 - f'(v_0)v_0$ . This equation is also the *i*-v characteristic of the sub-circuit shown in Fig. 1.7. This sub-circuit is called a *companion model*, of the nonlinear resistor. The element stamp of the companion model is then used to build the matrix of the linearized circuit, and the resulting linear system is solved. This process is repeated until the successive candidate solution points have converged to their final value.

#### 1.3.2 Dynamic Circuits

All the preceding has been for resistive circuits and we have focused on the solution at a single point in time, a so-called DC Analysis. In general, circuits include dynamic (L, C) elements, and we are interested in the response over time, a so-called Transient Analysis. This is done by using a *finite difference approximation* of the derivative, such as:

$$i = C \frac{dv}{dt} \approx C \frac{(v(t + \Delta t) - v(t))}{\Delta t}$$

(1.12)

By replacing all derivatives by their finite difference approximations, the circuit equations effectively become *algebraic*, rather than differential, and possibly nonlinear. Given the solution at time t, i.e., v(t) and i(t), these equations are then solved for  $v(t + \Delta t)$  and  $i(t + \Delta t)$ . Thus, by this operation of *time discretization*, the problem is reduced to solving a possibly nonlinear resistive network at every time-point, based on the use of another kind of *companion model* for the dynamic elements.

#### 1.4 CIRCUIT SIMULATION FLOW

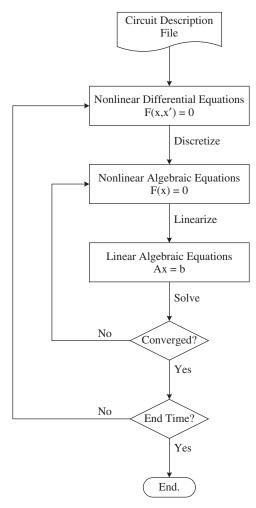

The flow-chart shown in Fig. 1.8 is useful to visualize the overall simulation flow inside a circuit simulator. The simulator repeatedly applies time discretization, element linearization, and matrix equation solution. In the following chapters, we will describe the many details, and pitfalls, of these various activities.

Figure 1.8: Overall circuit simulation flow.

#### 1.4.1 Analysis Modes

Circuit simulators offer different *analysis modes*. Berkeley's *The Spice Page*, at the web site:

http://bwrc.eecs.berkeley.edu/Classes/IcBook/SPICE

lists the following analysis modes for SPICE3:

• DC Analysis: Determines the DC operating point of the circuit with inductors shorted and capacitors opened. It is automatically performed prior to a Transient Analysis, to determine the initial conditions, and prior to an